PCIe 6.0 Controller IP

Filter

Compare

52

IP

from

7

vendors

(1

-

10)

-

PCIe 6.0 / CXL 3.0 PHY & Controller

- Innosilicon’s PCIe 6.0 and CXL 3.0 IP solutions combine high-performance controllers and PHYs, fully compliant with PCIe 6.0, CXL 3.0, and PIPE specifications

- These solutions deliver exceptional performance, low latency, power efficiency, and unparalleled flexibility, making them ideal for enterprise computing, data centers, cloud servers, AI and machine learning, storage expansion, and high-speed interconnect applications

-

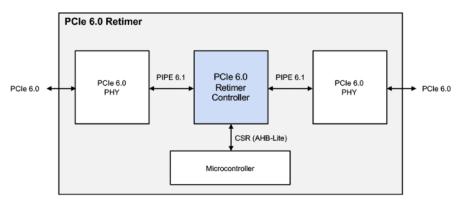

PCIe 6.0 Retimer Controller with CXL Support

- Designed to the latest PCI Express 6.0 (64 GT/s), and capable of supporting 32.0, 16.0, 8.0, 5.0 and 2.5 GT/s link rates

- Supports x1, x2, x4, x8 and x16 link widths

- CXL aware and supports sync header bypass

- Supports PIPE 5.2/6.1 compatible PHYs

- Optimized data-path for low latency insertion

-

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge and LTI & MSI Interfaces

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller EP/RP/DM/SW 128-1024 bits with AMBA bridge and Advanced HPC Features (Arm CCA)

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

Adds security Interfaces, features to PCIe 6.0 Premium controllers (Gen6)

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

Configurable controllers for PCIe 6.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

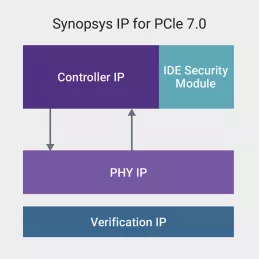

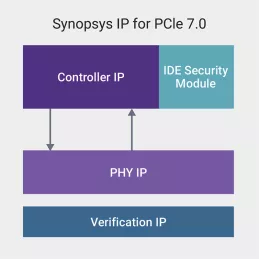

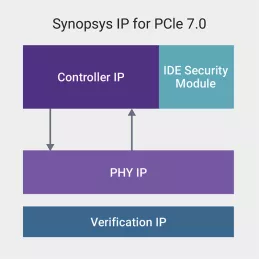

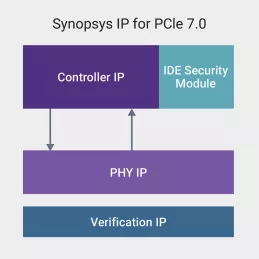

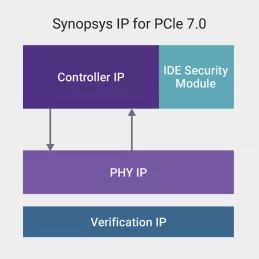

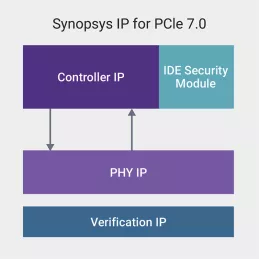

PCIe 6.0 Integrity and Data Encryption Security Module

- Compliant with PCI Express IDE specification

- Support for TDISP

- High-performance AES-GCM based packet encryption, decryption, authentication

- Seamless integration with Synopsys controllers via TLP packet-based interface

- FLIT mode support