PCIe 6 IP

Filter

Compare

303

IP

from

45

vendors

(1

-

10)

-

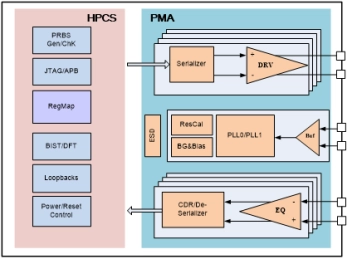

PCIe Gen 6 Phy

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- PCIe Gen 6 Phy IPPCIe Gen 6 Phy IPComprehensive real-time diagnostic, monitor, and test features

-

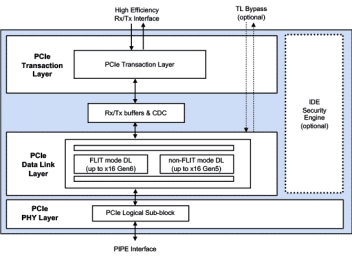

PCIe Gen 6 controller IP

- Designed to the latest PCI Express 6.0 (64 GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1/3.0 (8 GT/s), and PIPE 6.x (8, 16, 32, 64 and 128-bit) specifications

- Supports SerDes Architecture PIPE 10b/20b/40b/80b width

- Supports original PIPE 8b/16b/32b/64b/128b width

-

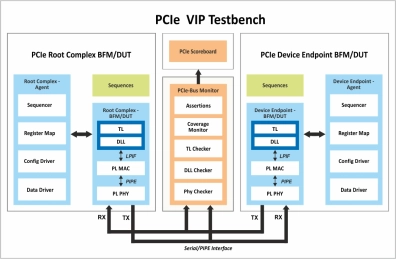

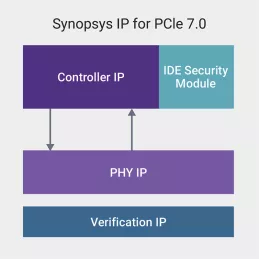

PCIe Gen 6 Verification IP

- Compliant with PCI Express Specifications 6.1 (64GT/s), 5.0 (32GT/s), 4.0 (16GT/s), 3.1 (8GT/s), 2.0 (5GT/s) and 1.1 (2.5GT/s).

- Support for 64.0 GT/s Data Rate per lane with backwards compatible.

- Support for new PAM4 Signalling and Gray Coding.

- Support for both Flit Mode & Non-Flit Mode.

-

PCIE 6.0/5.0/4.0/3.0/2.0

- Support PCI Expression Gen5 & Gen4 & Gen3 & Gen2 & Gen1

- Configurable differential voltage swing

- Embedded low jitter LC PLL with fixed bandwidth and output frequency

- PLL Frequency Lock detection

-

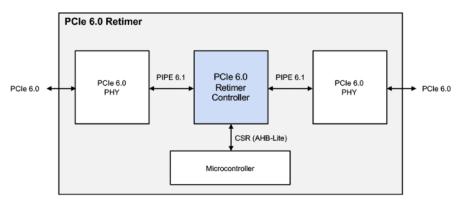

PCIe 6.0 Retimer Controller with CXL Support

- Designed to the latest PCI Express 6.0 (64 GT/s), and capable of supporting 32.0, 16.0, 8.0, 5.0 and 2.5 GT/s link rates

- Supports x1, x2, x4, x8 and x16 link widths

- CXL aware and supports sync header bypass

- Supports PIPE 5.2/6.1 compatible PHYs

- Optimized data-path for low latency insertion

-

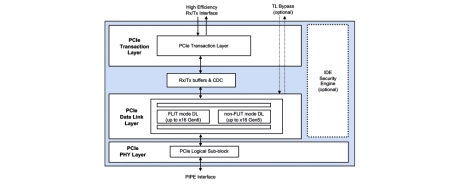

PCIe 6.1 Controller with AXI

- The PCI Express® (PCIe®) 6.1 Controller with AXI is configurable and scalable controller IP designed for ASIC implementation.

- The controller supports the PCIe 6.1 specification, including 64 GT/s data rates, PAM4 signaling, FLIT mode, and L0p power state.

-

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge and LTI & MSI Interfaces

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC