PCIe 4.0 PHY TSMC 16FF+ IP

Filter

Compare

11

IP

from

3

vendors

(1

-

10)

-

PCIe 4.0 PHY, TSMC 16FFPGL x8, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 PHY, TSMC 16FFPGL x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 PHY, TSMC 16FFPGL x16, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 4.0, 3.1, 2.1, 1.1, and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- Supports lane margining at the receiver

-

PCIe 4.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

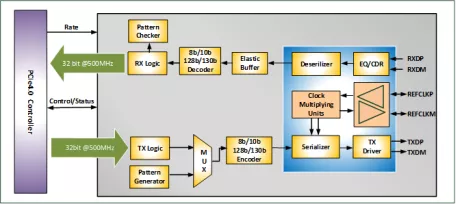

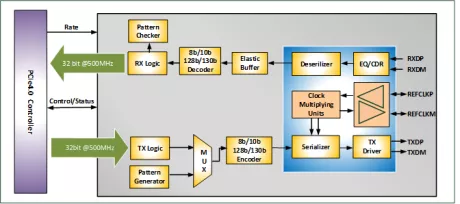

- Compliant with PCIe 4.0 Base Specification

- Compliant with PIPE 4.4

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s

- Supported physical lane width: x4

-

PCIe Gen4 PHY, x1-lane, RC/EP, TSMC 16FFC, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

PCIe Gen4 PHY, x4-lane, RC/EP, TSMC 16FFC, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

25G PHY, TSMC 16FFPGL x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 16FFC x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 16FFC x1 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 16FFC x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features