MIPI I3C Slave Controller IP

Filter

Compare

20

IP

from

10

vendors

(1

-

10)

-

MIPI I3C Slave Controller

- Compliant with the latest MIPI I3C specification

- Backward compatible with the I2C slave devices

- Supports all data rates up to 26.7 Mbps

- Optional High Data Rate messaging Modes (HDR)

-

MIPI I3C Slave v1.1 Controller IP enables efficient data flow for sensor integration.

- Compliant with the MIPI Alliance Specification for I3C Version 1.0

- Supports modes of Master – SDR [12.5 MHz], HDR DDR and HDR- Ternary (TSP, TSL) Modes

- Supports IBI, Hot Join

- Dynamic Addressing assignment support

-

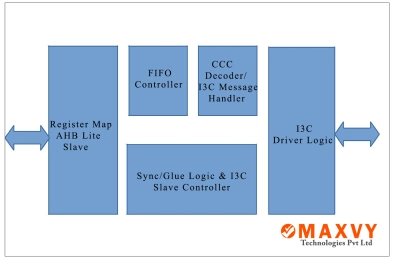

MIPI I3C Basic Slave Controller

- MIPI I3C(Improved Inter Integrated Circuit) is a two-wire bidirectional serial Bus for sensors communication

- The MIPI I3C interface has been developed to ease sensor system design architectures in mobile sensor and IoT / automotive sensor wireless products by providing a fast, low cost, low power

-

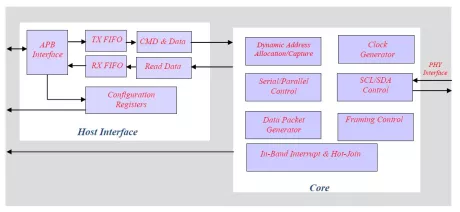

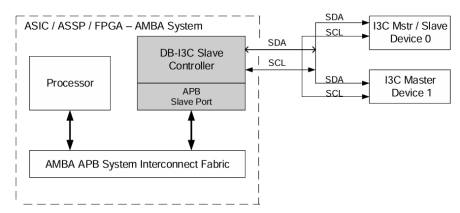

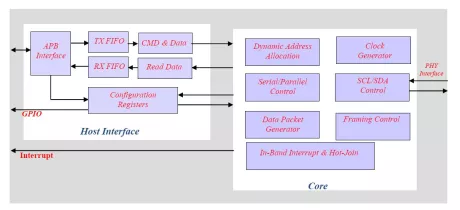

I3C Controller IP- Slave, Parameterized FIFO, APB Bus

- The DB-I3C-S-APB Controller IP Core interfaces a microprocessor via the AMBA APB Bus to an I3C Bus, compliant to the MIPI I3C – Improved Inter Integrated Circuit specification.

- The I3C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I3C devices as well as legacy I2C Slave devices.

-

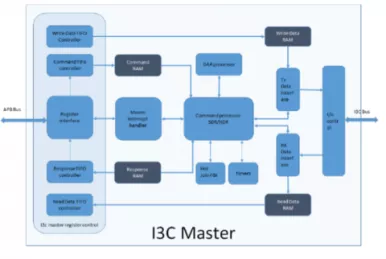

MIPI I3C Master Controller

- Compliant with the latest MIPI I3C specification

- Backward compatible with the I2C slave devices

-

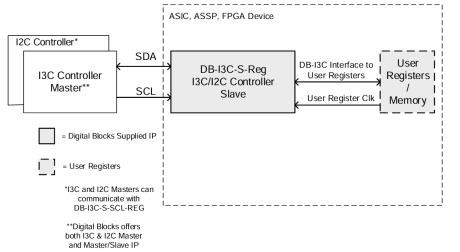

I3C Controller IP – I3C / I2C Slave, Configure User Registers, no CPU Host Required

- The DB-I3C-S-REG is an I3C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs requiring the configuration & control of registers with no local host processor.

- The DB-I3C-S-REG processes the I3C protocol & physical layers, and receives & transmits bytes with respect to the I3C payload to / from User Registers within an ASIC / ASSP / FPGA device.

- The DB-I3C-S-REG Controller implements the Slave-Transmit and Slave-Receive protocol according to the MIPI I3C-Basic-Spec ver1_0 specification.

-

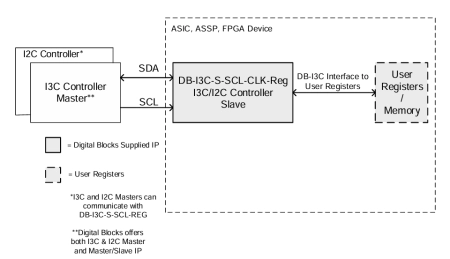

I3C Controller IP – I3C / I2C Slave, SCL Clock only, Configure User Registers, no CPU Host Required

- The DB-I3C-S-SCL-CLK-REG is an I3C Slave Controller IP Core focused on low power, low noise, low VLSI footprint ASIC / ASSP designs requiring the configuration & control of registers with no free running clock.

- The DB-I3C-S-SCL-CLK-REG processes the I3C protocol & physical layers, and receives & transmits bytes with respect to the I3C payload to / from User Registers within an ASIC / ASSP / FPGA device.

- The DB-I3C-S-SCL-CLK-REG Controller implements the Slave-Transmit and Slave-Receive protocol according to the MIPI I3C-Basic-Spec-ver1_0 specification.

-

MIPI I3C Master v1.1 Controller IP offers impressive data transmission capacity for sensor integration.

- Compliant with the MIPI Alliance Draft Specification for I3C Version 0.5 Revision 1.0

- Supports all modes of Master – SDR [12.5 MHz], HDR and HDR-DDR, I2C Modes.

- Supports interrupt handling.

- Enables peer to peer communication.

-

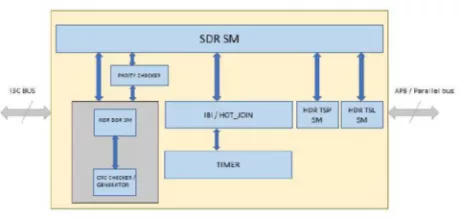

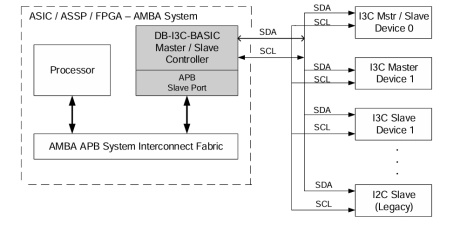

I3C Controller IP – Master / Slave, Parameterized FIFO, APB Bus. I3C Basic Specification Design

- Master / Slave MIPI I3C Controller

- Supports following I3C bus speeds: Single Data Rate (SDR) - up to 12.5 MHz

- I3C Communications Support: I3C SDR / Broadcast / Direct Messages; Legacy I2C Message

-

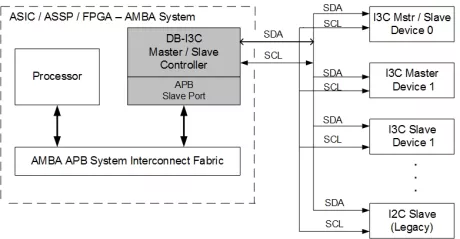

I3C Controller IP – Master / Slave, Parameterized FIFO, APB Bus

- The DB-I3C-MS-APB Controller IP Core interfaces a microprocessor via the AMBA APB Bus to an I3C Bus, compliant to the MIPI I3C – Improved Inter Integrated Circuit specification.

- The I3C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I3C devices as well as legacy I2C Slave devices.

- The DB-I3C-MS-APB is a I3C Controller supporting I3C SDR / Broadcast / Direct Messages, Legacy I2C Message, and I3C HDR Mode (optionally).