MACsec Protocol Engine IP

Filter

Compare

24

IP

from

6

vendors

(1

-

10)

-

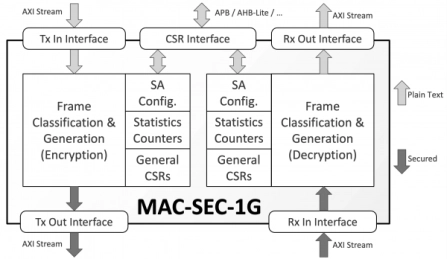

MACsec Protocol Engine for 10/100/1000 Ethernet

- The MAC-SEC-1G IP core implements a compact and configurable custom-hardware protocol engine for the IEEE 802.1AE (MACsec) standard.

- It supports all cipher suites provisioned by the MACsec standard and the VLAN-in-Clear improvement and is silicon- and performance-optimized for networks operating up to 1Gbps.

-

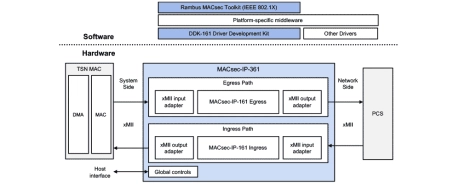

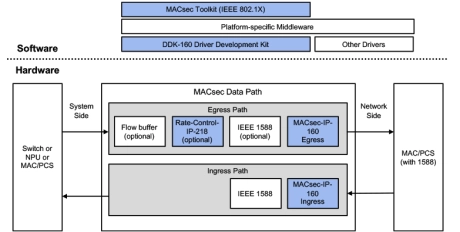

1G to 50G Single-Port MACsec Engine with xMII interface and TSN support

- MACsec solution for integration between MAC and PCS side supporting 1GbE to 50GbE rates with optional TSN support (including IEEE803.2br).

- For MACsec function integrates the MACsec-IP-161 with all IEEE MACsec standards supported. Optional Cisco ClearTags.

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management

-

1G to 50G Single-Port MACsec Engine with TSN support

- Complete and compliant MACsec Packet Engine for rates from 1GbE to 50GbE with TSN support (including IEEE803.2br).

- All IEEE MACsec standards supported (incl. IEEE802.1AE-2018). Optional Cisco ClearTags.

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management

-

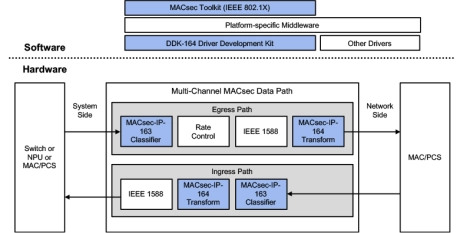

800G Multi-Channel MACsec Engine with TDM Interface

- Complete and fully compliant MACsec Packet Engine with classifier and transformation engines for rates of 100 to 800 Gbps, up to 64 channels, ready for FlexE

- All IEEE MACsec standards supported (including IEEE802.1AE-2018). Optional inclusion of Cisco extensions, IPsec ESP tunnel and transport mode with AES-GCM cipher

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management

-

1G to 100G Single-Port MACsec Engine

- Complete HW/SW system.

- Driver Development Kit.

- High-speed MACsec Frame Engine

- Silicon-proven implementation

- Fast and easy to integrate into SoCs.

- Flexible layered design.

-

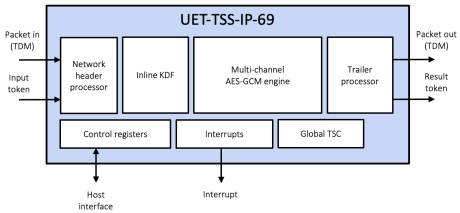

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

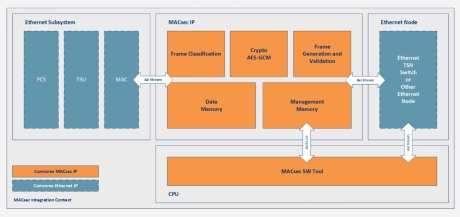

10M MACsec

- The MACsec IP provides Ethernet Layer 2 Security for port authentication, data confidentiality and data integrity as standardized in IEEE 802.1AE.

- It protects components in Ethernet networks especially very low-speed Ethernet used in automotive, industrial, and consumer applications.

- The MACsec IP is a fully compliant solution that provides line-rate encryption and is optimized for the smallest area size.

-

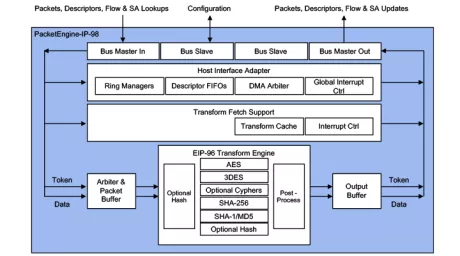

Multipurpose Security Protocol Accelerator

- Highly configurable security accelerator

- Support for all ciphers, hashes and MAC algorithms used in major protocols such as IPsec, SSL/TLS/DTLS, Wi-Fi, 3GPP LTE/LTE-A, SRTP, MACsec

- Cipher algorithms: AES, DES/3DES, ChaCha20, MULTI2, KASUMI, SNOW 3G, ZUC

- Cipher modes: ECB, CBC, CTR, OFB, CFB, f8, XTS, UEA1, UEA2, 128-EEA1, 128-EEA2, 128-EEA3

-

Multipurpose Security Protocol Accelerator - Functional Safety ASIL B support

- Highly configurable security accelerator

- Support for all ciphers, hashes and MAC algorithms used in major protocols such as IPsec, SSL/TLS/DTLS, Wi-Fi, 3GPP LTE/LTE-A, SRTP, MACsec

- Cipher algorithms: AES, DES/3DES, ChaCha20, MULTI2, KASUMI, SNOW 3G, ZUC

- Cipher modes: ECB, CBC, CTR, OFB, CFB, f8, XTS, UEA1, UEA2, 128-EEA1, 128-EEA2, 128-EEA3

-

Multi-Protocol Engine with Classifier, Look-Aside, 5-10 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP and MACsec Packet Engine with virtualization, caches classifier and Look-Aside interface for multi-core application processors

- 5-10 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP, DPDK, Linux Crypto