Lightweight Multi-Format Video Encoder IP

Filter

Compare

120

IP

from

34

vendors

(1

-

10)

-

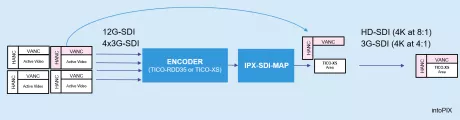

SDI Mapper for TICO-RDD35 & TicoXS (JPEGXS) lightweight codecs

- Manage both the TX & RX

- Manage the insertion of the TICO-RDD35 or JPEG-XS detection box over the active area of the SDI

-

TicoXS | JPEG XS HD Encoder / Decoder IP-cores

- Near-Lossless up to 6:1.

- Visually lossless up to 12:1

- Color format : RGB,YUV, YCbCr, 444 / 422 /420 / monochrome

- Smooth lossy compression beyond

-

TicoXS | JPEG XS 4K Encoder / Decoder IP-core

- Near-Lossless up to 6:1.

- Visually lossless up to 10:1

- Smooth lossy compression beyond

-

TICO Lightweight HD Encoder

- Visually Lossless quality up to 4:1

- 4:2:2 ; 4;4:4 & 8,10,12bit

- CBR (VBR as option)

-

Video Transport over IP-Cores

- HD & 4K over 1G or 10G network

- SMPTE2022 1/2 & 5/6

- Easy way to accelerate time to market with future-proof solutions

- Interoperable with VSF TR recommendations

-

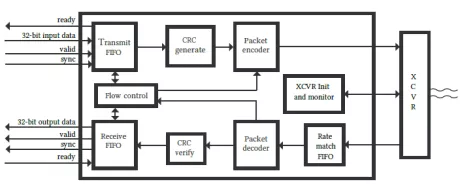

Serial FPDP

- VITA 17.1-2003 Compliant

- Conforms to FC-PH disparity rules

- Multi-lane channel bonding wrapper

- Independent data / system clock domains

-

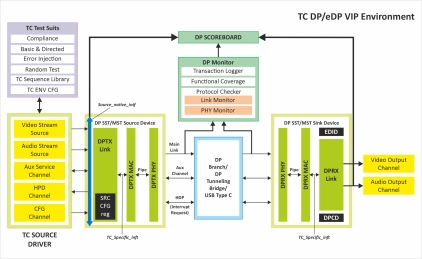

eDP 2.0 Verification IP

- The eDP 2.0 Verification IP provides an effective & efficient way to verify the components interfacing with the eDP interface of an ASIC/FPGA or SoC.

- The eDP VIP is fully compliant with the Standard eDP Version 2.0 specifications from VESA.

- This VIP is a lightweight VIP with an easy plug-and-play interface, so that there is no hit on the design time and the simulation time.

-

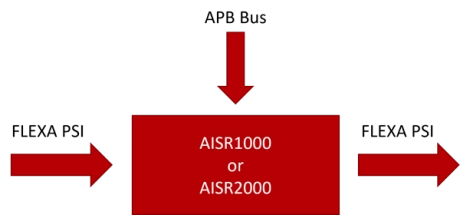

High-efficiency, AI-based super resolution IP

- The AI-SR series IPs offer super resolution solutions for enhancing video quality and pixel resolution, primarily used for post-processing or display applications.

- Currently consisting of AISR1000 and AISR2000 IPs, this series enables generation or transfer of low-resolution sources for bandwidth reduction and performance improvement, while ensuring high-quality, high-resolution displays at the edge.

-

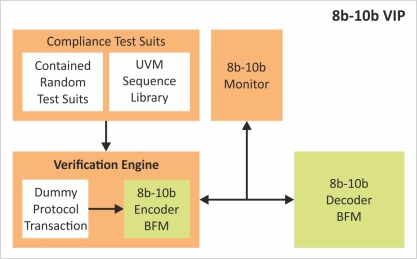

8b-10b Verification IP

- Encoding of 8-bit bytes into 10-bit symbols.

- Decoding of 10-Bit symbols into 8-bit Bytes.

- Encoding of 12 special (K) characters in addition to the 256 possible combinations.

- Encoder tracks running disparity, ensuring that consecutive symbols have correct disparity.

-

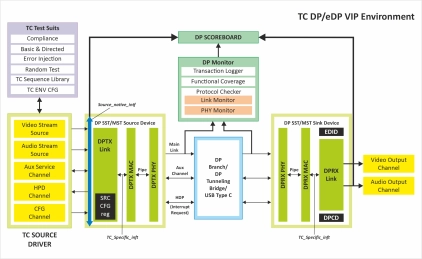

eDP 1.5 Verification IP

- Fully compliant with VESA Embedded DisplayPort (eDP) Standard 1.5 Specification

- Supports power saving feature:- Panel Self Refresh features PSR/PSR2, PR, Adaptive sync, and backlight control.

- Supports HDCP version 1.4, 2.2 and 2.3

- Supports Alternative Scrambler Seed Reset (ASSR)

- TPS4 with ASSR is supported