I2C Slave Controller IP

Filter

Compare

76

IP

from

26

vendors

(1

-

10)

-

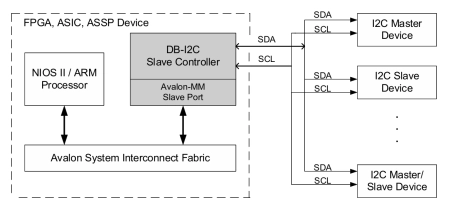

I2C Controller IP – Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-S-AHB Controller IP Core interfaces a NIOS II, ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the Avalon System Interconnect Fabric to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

-

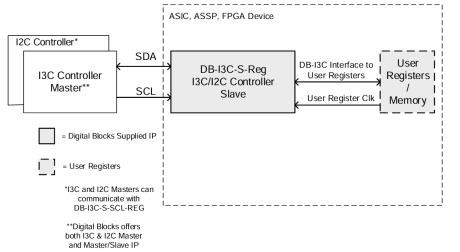

I3C Controller IP – I3C / I2C Slave, Configure User Registers, no CPU Host Required

- The DB-I3C-S-REG is an I3C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs requiring the configuration & control of registers with no local host processor.

- The DB-I3C-S-REG processes the I3C protocol & physical layers, and receives & transmits bytes with respect to the I3C payload to / from User Registers within an ASIC / ASSP / FPGA device.

- The DB-I3C-S-REG Controller implements the Slave-Transmit and Slave-Receive protocol according to the MIPI I3C-Basic-Spec ver1_0 specification.

-

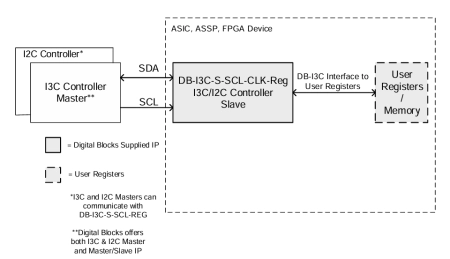

I3C Controller IP – I3C / I2C Slave, SCL Clock only, Configure User Registers, no CPU Host Required

- The DB-I3C-S-SCL-CLK-REG is an I3C Slave Controller IP Core focused on low power, low noise, low VLSI footprint ASIC / ASSP designs requiring the configuration & control of registers with no free running clock.

- The DB-I3C-S-SCL-CLK-REG processes the I3C protocol & physical layers, and receives & transmits bytes with respect to the I3C payload to / from User Registers within an ASIC / ASSP / FPGA device.

- The DB-I3C-S-SCL-CLK-REG Controller implements the Slave-Transmit and Slave-Receive protocol according to the MIPI I3C-Basic-Spec-ver1_0 specification.

-

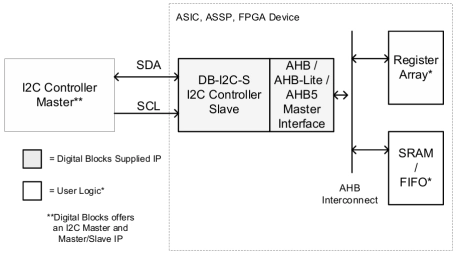

I2C Controller IP – Slave, Parameterized FIFO, AHB Master Interface (I2C2AHB)

- The DB-I2C-S-AHB-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required), and an AHB Master interface for read/write to the user system.

- The DB-I2C-S-AHB-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via a bridge AHB Master Interface to user registers or memory.

-

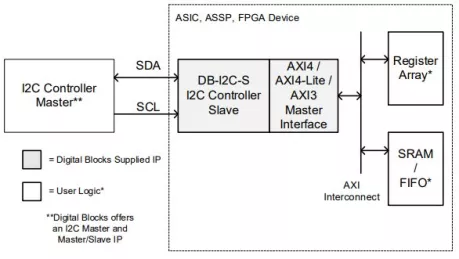

I2C Controller IP – Slave, Parameterized FIFO, AXI Master Interface (I2C2AXI)

- The DB-I2C-S-AXI-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required), and an AXI Master interface for read/write to user system.

- The DB-I2C-S-AXI-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via the bridge AXI Master Interface to user registers or memory.

-

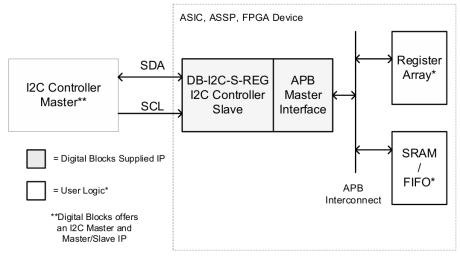

I2C Controller IP – Slave, Parameterized FIFO, APB Master Interface (I2C2APB)

- The DB-I2C-S-APB-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required).

- The DB-I2C-S-APB-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via a bridge APB Master Interface to user registers or memory.

-

I2C Bus Master / Slave Controller Interface with FIFO

- Conforms to v.3.0 of the I2C specification

- Master mode

- Master operation

- Master transmitter

-

I2C Controller IP – Slave, Parameterized FIFO, AHB Bus

-

The DB-I2C-S-AHB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 2.0/3.0 AHB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-AHB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-AHB Controller IP Core embedded within an integrated circuit device.

-

-

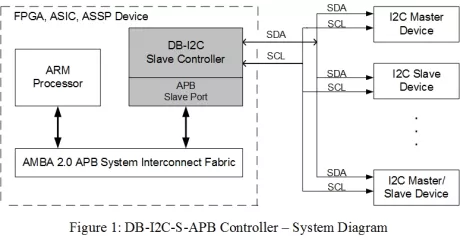

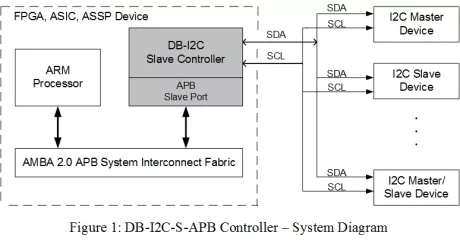

I2C Controller IP – Slave, Parameterized FIFO, APB Bus

- The DB-I2C-S-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high performance microprocessor via the AMBA 2.0 APB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

- The DB-I2C-S-APB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-APB Controller IP Core embedded within an integrated circuit device.