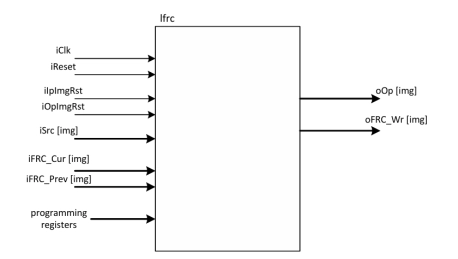

Frame Rate Conversion IP

Filter

Compare

19

IP

from

13

vendors

(1

-

10)

-

Linear Frame Rate Converter

- 8/10/12-bit 4:2:2 or 4:4:4 processing

- Low latency (~2 lines)

- Fully synchronous design

-

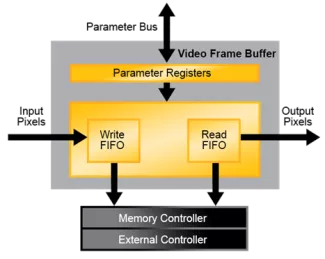

Video Frame Buffer

- Single color, YCbCr 4:2:2, YcbCr 4:4:4 and RGB video formats

- Input and output resolutions of 64x64 to 4Kx4K pixels

- Serial and parallel pixel processing

- Frame rate conversion

-

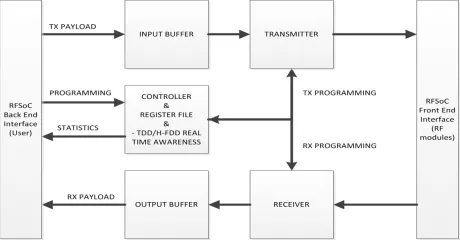

High Throughput Rate OFDM Baseband PHY Processor

- Custom OFDMA system based on 802.16e standard features.

- Complete Back-end User IF for primitive MAC integration.

-

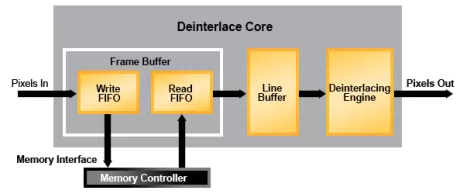

Deinterlacer

- Supports for single color, YCbCr4:2:2, YcbCr4:4:4 and RGB video formats.

- Supports serial and parallel deinterlacing.

- Supports weave, bob, intra and inter motion adaptive deinterlacing algorithms.

- Supports frame rate conversion.

-

Polyphase Video Scaler

- High quality polyphase algorithm

- High resolution support from 240×240 to 4k

- Processing up to 4k@60 fps

- Features dynamic resizing built-in anti-aliasing

-

Image Signal Processor IP - Ultra-low power image signal processing for AIoT and wearable markets

- Supports DVP Input Interface

- Input color formats: 8-bit, 10-bit, 12-bit Bayer; 8-bit, 10-bit YUV BT.601, BT.656; 8-bit, 10-bit monochrome

- SW Register Configuration: 32-bit AHB Slave

- Frame rate control, configurable output FPS range from 60fps to 1fps

-

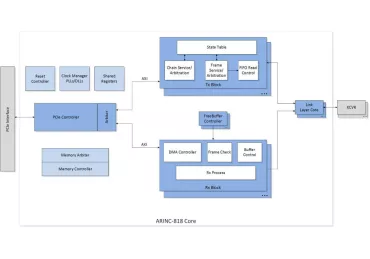

ARINC 818 Streaming IP Core

- Flexible video pixel bus input with synchronization signals (video_active, vsync, hsync) that supports a wide range of pixel depths and number of parallel pixels

- Compatible with all FC line rates up to 10G (incl. non-standard rates)

- Core handles synchronization and clock crossing into the FC clock domain. User clock can be asynchronous to the FC clock

- Automatic creation and maintenance of the Object 0 and container header

-

Single-core video encoder - AV1, HEVC, AVC

- YUV420/YUV422/YUV444

- 8/10-bit depth

- I/P/B-frame

- Frame buffer compression

- Multi-instances

-

ISDB-S3 modulator

- The Commsonic CMS0070 ISDB-S3 Modulator with integrated LDPC encoder has been designed specifically to address the requirements of the ARIB STD-B44 advanced wide-band digital satellite standard.

- The core provides all the necessary processing steps to modulate a single transport stream (or baseband frame) into a complex I/Q signal for input to a pair of DACs, or an interpolating DAC device such as the AD9857(or AD9957). Optionally, the output can be selected as an IF to supply a signal DAC.

-

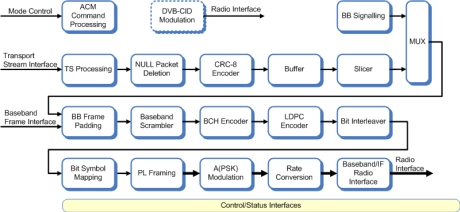

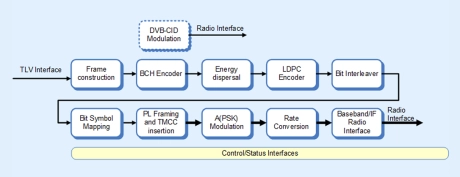

DVB-S2 modulator

- The CMS0025 DVB-S2/S2X Modulator with integrated LDPC encoder has been designed specifically to address the requirements of the ETSI DVB-S2 forward-link satellite standard (EN 302 307), section-1 together with the section-2 extensions (DVB-S2X), with additional support for DVB-S2X VLSNR operation. The core can operate in CCM and VCM/ACM modes.

- The core provides all the necessary processing steps to modulate a single transport stream (or baseband frame) into a complex I/Q signal for input to a pair of DACs, or an interpolating DAC device such as the AD9857(or AD9957). Optionally, the output can be selected as an IF to supply a signal DAC.