Elliptic Curve Cryptography Accelerator IP

Filter

Compare

13

IP

from

6

vendors

(1

-

10)

-

High-Speed Elliptic Curve Cryptography Accelerator for ECDH and ECDSA

- Fully digital design

- Portable to any ASIC or FPGA technology

- Fully standard compliant

- Easy to integrate

-

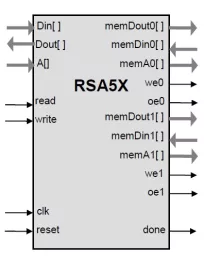

Scalable RSA and Elliptic Curve Accelerator

- The core implements the exponentiation operation of the RSA cryptography Q = Pk.

- The operands for the exponentiation: k and P as well as the modulus are programmed into the memory and the calculation is started.

- Once the operation is complete, the result Q can be read through the interface.

-

ECC Secure Accelerator - High-performance ECC IP with advanced physical security

High-performance ECC IP with advanced physical security

-

ECC Secure Accelerator - Compact and Secure ECC IP Core for Resource-Constrained Devices

- Compact and Secure ECC IP Core for Resource-Constrained Devices

-

Crypto Box Toolset Secure Accelerator

- The Hybrid Crypto Box IP core is a comprehensive, high-efficiency cryptographic solution that combines RSA, ECC, AES, and SHA-2/HMAC with a built-in accelerator for post-quantum algorithms such as ML-KEM (Kyber) and ML-DSA (Dilithium). Designed for embedded systems with balanced resource constraints, it enables secure key exchange, digital signatures, authenticated encryption, and hashing, future-proofed for the quantum era.

-

Agile Post Quantum Crypto (PQC) Public Key Accelerator - NIST algorithms

- Offloads the computationally intensive parts of public key cryptography

- Support for ARM® AMBA® AHB™/AXI™ and synchronous RAM interfaces

- Integer operations (512-, 768-, 1024-, 1536-, 2048-, 3072-, and 4096-bit)

- ECC-GF(p) operations (160, 192, 224, 256, 384, 512 and 521-bit)

-

Agile ECC/RSA Public Key Accelerator with 32-bit ALU

- Offloads the computationally intensive parts of public key cryptography

- Support for ARM® AMBA® AHB™/AXI™ and synchronous RAM interfaces

- Integer operations (512-, 768-, 1024-, 1536-, 2048-, 3072-, and 4096-bit)

- ECC-GF(p) operations (160, 192, 224, 256, 384, 512 and 521-bit)

-

Agile ECC/RSA Public Key Accelerator with 128-bit ALU

- Offloads the computationally intensive parts of public key cryptography

- Support for ARM® AMBA® AHB™/AXI™ and synchronous RAM interfaces

- Integer operations (512-, 768-, 1024-, 1536-, 2048-, 3072-, and 4096-bit)

- ECC-GF(p) operations (160, 192, 224, 256, 384, 512 and 521-bit)

-

Public Key Accelerator

- Modular exponentiation operations with up to 4096-bit modulus

- Prime field ECC operations with up to 571-bit modulus

- Fastest implementation is 58 kGE and 68 Op/s for 2048-bit RSA, 431 Op/s for 1024-bit RSA, 150 Op/s for 384-bit scalar multiplication

- Smallest implementation is 33 kGE and 67 Op/s for 1024-bit RSA, 24 Op/s for 384-bit scalar multiplication

-

32-bit Public Key Accelerator

- Offloads the computationally intensive parts of public key cryptography

- Support for ARM® AMBA® AHB™/AXI™ and synchronous RAM interfaces

- Integer operations (512-, 768-, 1024-, 1536-, 2048-, 3072-, and 4096-bit)

- ECC-GF(p) operations (160, 192, 224, 256, 384, 512 and 521-bit)