Display Engine IP

Filter

Compare

42

IP

from

18

vendors

(1

-

10)

-

2D GPU IP Core - Target Display Resolution: 8K

- Xwindow (EXA)

- Hardware Composer (HWC)

- DirectFB

- Pixel Rate (Pixels/Cycle): 4

- Target Display Resolution: 8K

- Direct 3D Tile Status and Buffer Option: yes

- Formats Support: RGB & YUV FP16/32

-

2D GPU IP Core - Target Display Resolution: 4K

- Xwindow (EXA)

- Hardware Composer (HWC)

- DirectFB

- Pixel Rate (Pixels/Cycle): 2

- Target Display Resolution: 4K

- Direct 3D Tile Status and Buffer Option: yes

- Formats Support: RGB & YUV FP16/32

-

2D GPU IP Core - Target Display Resolution: 2.5K~4K

- Xwindow (EXA)

- Hardware Composer (HWC)

- DirectFB

- Pixel Rate (Pixels/Cycle): 4

- Target Display Resolution: 2.5K~4K

- Direct 3D Tile Status and Buffer Option: yes

- Formats Support: RGB & YUV Limited

-

Display controller for dual-display

- Scan directions: 90/180/270° rotation, horizontal/vertical flip

- Multiple layers (alpha blend) with configurable mapping

-

2D GPU IP Core - Target Display Resolution: 4K

- Xwindow (EXA)

- Hardware Composer (HWC)

- DirectFB

- Pixel Rate (Pixels/Cycle): 4

- Target Display Resolution: 4K

- Direct 3D Tile Status and Buffer Option: yes

- Formats Support: RGB & YUV

-

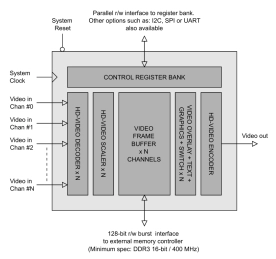

HD Multi-window Video Processor IP Core

- This brief specification describes the operation of the HD Multi-window Video Processor (evaluation) IP Core.

- The IP Core is provided as a netlist in either EDIF, Verilog or VHDL formats.

-

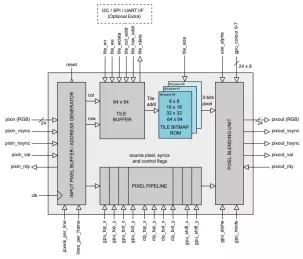

Graphics Processor Overlay IP Core

- Technology independent soft IP Core for FPGA, ASIC and SoC devices

- Supplied as human-readable VHDL (or Verilog) source code

-

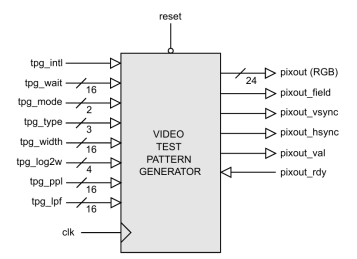

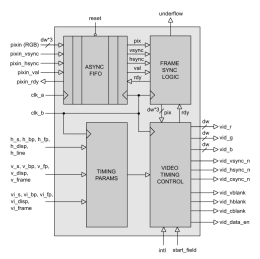

Video Test Pattern Generator

- Pixels and syncs are generated on a rising clock-edge when pixout_val is high and pixout_rdy is high.

- The signal pixout_vsync is active high when the first pixel of a frame is output.

- The signal pixout_hsync is active high when the first pixel of a line is output.

- The pixout_field flag indicates either an odd or even field when interlaced mode is enabled.

-

Video Timing Generator

- The VID_TIMING_GEN IP Core is a fully configurable video timing generator with the ability to support any video resolution up to 216 x 216 pixels in size.

- The module is compatible with a wide range of video DACs, encoders and transmitters and provides a flexible solution for displaying digital or analogue video on an external TV, monitor or flat panel display.

- The module is capable of clock speeds in excess of 400 MHz on some FPGA platforms, making it ideal for the latest generation HD and UHD video solutions.

-

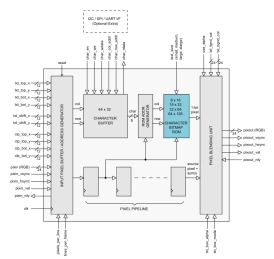

Text Overlay Module (OSD)

- The TXT_OVERLAY IP Core is a highly versatile On Screen Display (OSD) module that allows text and bitmap graphics to be inserted over RGB video.

- The module supports a wide range of text effects and the programming interface is very simple.

- Text is written to a character buffer which is mapped (via a bitmap ROM) directly to the display.