DDR3/2 SDRAM IP

Filter

Compare

5

IP

from

4

vendors

(1

-

5)

-

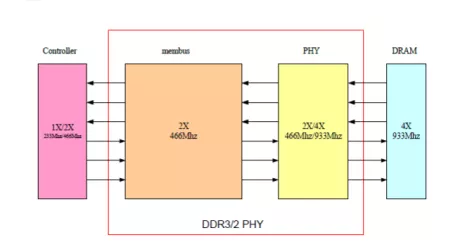

DDR3/2 PHY - TSMC 40LP25

- When combined with a Synopsys DDR memory or protocol controller and verification IP, Synopsys provides a complete DDR3/2 interface IP solution

- Scalable architecture that supports the speed range from DDR2-667 up to DDR3-2133

- Support for DDR3L (1.35V DDR3)

- Support for DDR2 and DDR3 DIMMs

-

DDR3/2 PHY

- ? DDR2/DDR3/DDR3U/DDR3L/LVCMOS operating modes

- ? Compatible with JEDEC standard DDR2/DDR3/DDR3U/DDR3L SDRAMs

- ? Scalable performance from DDR2-667 through DDR3-1600

- ? Maximum controller clock frequency of 400MHz resulting in maximum SDRAM data rate of 1600 Mbps

-

DDR PHY

- Dolphin's hardened DDR4/3/2 SDRAM PHY and LPDDR5/4x/4/3/2 SDRAM PHY IP is a silicon-proven, Combo PHY supporting speeds up to 4266 Mbps.

- It is fully compliant with the DFI 4.0 specification, and features include slew rate control, per-bit de-skew, gate training, read and write leveling and built-in self test (BIST).

- In addition, our PHY IP is optimized to provide a complete solution when combined with Dolphin's DDRx and LPDDRx SDRAM Memory Controller IP.

-

DDR3/ DDR2 Combo PHY IP - 1866Mbps (Silicon Proven in UMC 40LP)

- Supports DDR3/DDR2 SDRAM

- DDR3 JEDEC standard 1.5v I/O (SSTL_15- compatible)

- DDR2 JEDEC standard 1.8v I/O (SSTL_18- compatible)

- 16 bits width, Single Channel DDR3/DDR2 SDRAM Interface.

-

High Performance DDR 3/2 Memory Controller IP

- Supports DDR3/DDR2 SDRAM

- 16 bits width DDR2/DDR3 SDRAM Interface

- Memory Clock up to 462MHz, DFI Clock up to 462MHz

- Support DDR2 667/800/1066 and DDR3 667/800/1066/1333/1600/1866