16nm SerDes IP

Filter

Compare

23

IP

from

3

vendors

(1

-

10)

-

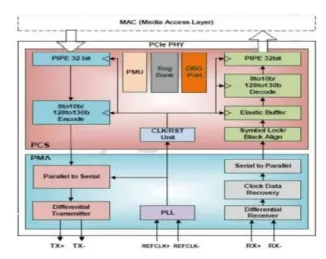

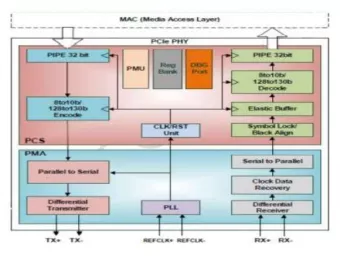

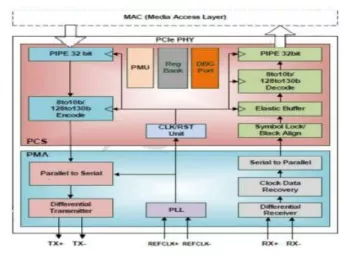

PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

- Compatible with PCIe base Specification

- Full compatible with PIPE3.0 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

PCIe 4.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

- Compliant with PCIe 4.0 Base Specification

- Compliant with PIPE 4.4

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s

- Supported physical lane width: x4

-

PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

- Compliant with PCIe 5.0 Base Specification

- Compliant with PIPE 5.1

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s, 16.0 GT/s and 32GT/s

- Supported physical lane width: x4

-

TSMC CLN16FF+GLLVT 16nm Clock Generator PLL - 300MHz-1500MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

TSMC CLN16FF+GLLVT 16nm Clock Generator PLL - 600MHz-3000MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

TSMC CLN16FF+GLLVT 16nm Clock Generator PLL - 1200MHz-6000MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

TSMC CLN16FF+LLLVT 16nm Clock Generator PLL - 300MHz-1500MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

TSMC CLN16FF+LLLVT 16nm Clock Generator PLL - 600MHz-3000MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

TSMC CLN16FF+LLLVT 16nm Clock Generator PLL - 1200MHz-6000MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.