WIDE IO2 Synthesizable Transactor provides a smart way to verify the WIDE IO2 component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's WIDE IO2 Synthesizable Transactor is fully compliant with standard JESD229-2 Specification and provides the following features.

WIDE IO2 Synthesizable Transactor

Overview

Key Features

- Supports 100% of WIDE IO2 protocol standard JESD229-2

- Supports all the WIDE IO2 commands as per the specs

- Quickly validates the implementation of the WIDE IO2 standard JESD229-2

- Support programmable burst lengths: 4,8

- Checks for following:

- Check-points include power up, initialization and power off rules

- State based rules, active command rules

- Read/Write command rules etc

- All timing violations

- Supports all mode registers programming

- Supports write data mask and data bus inversion

- Supports GPIO mode test access

- Supports post package repair

- Supports power down features

- Supports TRR mode

- Supports full-timing as well as behavioral versions in one model

- Models, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

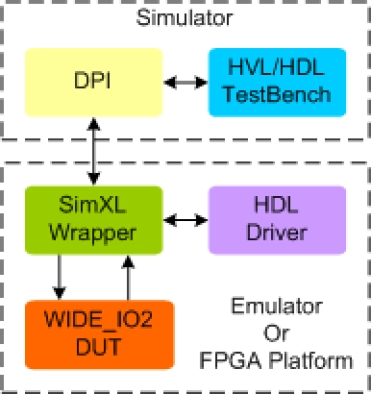

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the WIDE IO2 testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Technical Specifications

Short description

WIDE IO2 Synthesizable Transactor

Vendor

Vendor Name