PowerPC System Controller

Key Features

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Supports PowerPC 603, 604, 740, 750, MPC8260, 860 microprocessors.

- Fully integrated single chip design provide complete system level functions for all external data access.

- Replaces multiple discrete devices on the system.

- Flexible design adaptive to different system requirements.

- Two different clock domains for CPU and PCI bus interface.

- Supports concurrent data transfer between CPU, System memory, DMA and PCI bus.

- System control register distributed in each functional blocks.

- On-chip connection to user-defined logic blocks.

- PCI specification 2.2 compliant.

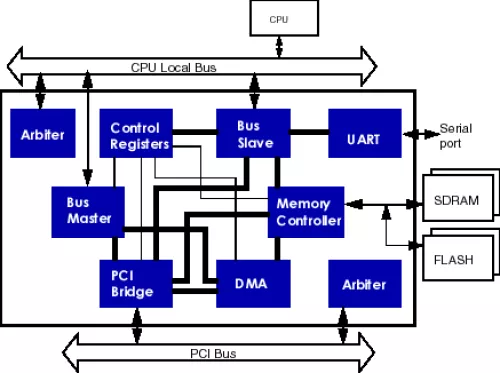

Block Diagram

Technical Specifications

Foundry, Node

ASIC and FPGA

Availability

now

UMC

Pre-Silicon:

500nm