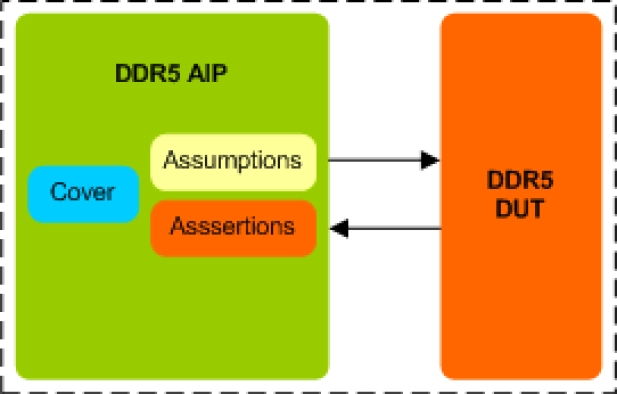

DDR5 Assertion IP provides an efficient and smart way to verify the DDR5 designs quickly without a testbench. The SmartDV's DDR5 Assertion IP is fully compliant with standard DDR5 Specification.

DDR5 Assertion IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

DDR5 Assertion IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.