10-Bit 64MHz 1.2V 1.9mW delta-sigma ADC, CMOS 130nm

Overview

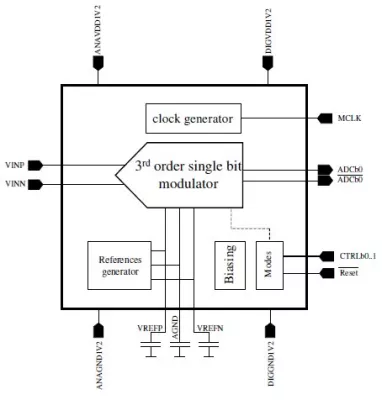

The nSAD_ST130M_1V2_AD10b64M is a 64MS/s, 9.9 ENOB, power efficient Sigma Delta ADC designed on the ST 130 M technology. Built around a fully-differential 3rd-order single-bit low-pass modulator, it consumes 1.9mW on silicon, reaching an energy efficiency of 31fJ/conversion-step.

Key Features

- STMicroelectronics 130nm CMOS mixed-mode process

- Single 1.2V supply

- 64 MHz modulator clock rate

- 700 mVpp_diff input dynamic range

- Modulator signal bandwidth = 1 MHz

- SNRpeak = 62.3dB @ Fin = 100kHz

- SNDRpeak = 61.3dB @ Fin = 100kHz

- SFDRpeak = 80dBc @ Fin = 100kHz

- THDpeak = -75dBc @ Fin = 100kHz

- Fully internal reference voltage generator and bias circuitry

- only 1.9mW typical at 64MHz including reference generator and biasing

- 0.15 mm2 core area including reference generator, biasing

Block Diagram

Applications

- Very low power communications (Zigbee, Bluetooth LE)

- Very low power industrial control and instrumentation

- Battery powered systems

- Automotive and logistics equipment

Technical Specifications

Short description

10-Bit 64MHz 1.2V 1.9mW delta-sigma ADC, CMOS 130nm

Vendor

Vendor Name

Foundry, Node

ST 130nm MM

Maturity

Silicon proven

Availability

Now