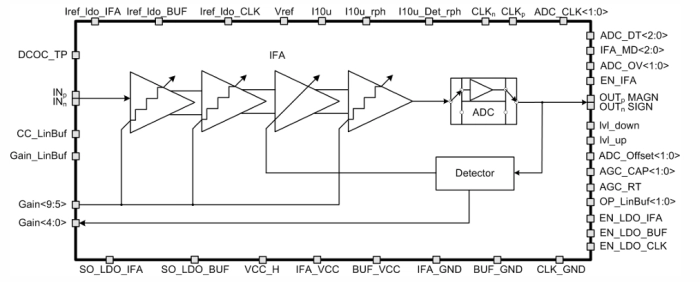

IFA consists of 4-stage amplifier with tunable gain, AGC system, linear output buffer for differential analog output, analog-digital converter for digital output and a detector of output level.

The amplifier has differential inputs and outputs, and consists of 4 stages. Gain is sequentially reduced from the last stage to the first stage. This method allows to keep a low noise figure in wide gain range.

The output voltage maintained by AGC system at differential load 200 Ohm:

- for sinusoidal signal is 200 mV (p-p);

- for noise signal is 480 mV (p-p).

The block is fabricated on AMS035 BiCMOS 0.35 um technology

0.8 to 25 MHz Intermediate-frequency amplifier

Overview

Key Features

- AMS035 BiCMOS 0.35 um

- Wide gain range (0…64 dB)

- Low group delay time ripple vs. frequency and gain

- Analog and digital output modes

- Built-in AGC detector with internal capacitor

- Built-in DC offset compensation mode in each stage and in the output buffer

- AGC detector threshold adjustment in the digital mode

- Portable to other technologies (upon request)

Block Diagram

Applications

- Receivers

- Navigation systems

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

0.8 to 25 MHz Intermediate-frequency amplifier

Vendor

Vendor Name

Foundry, Node

AMS BiCMOS 0.35 um

Maturity

silicon proven

Availability

Now