Format Conversion IP

Welcome to the ultimate Format Conversion IP hub! Explore our vast directory of Format Conversion IP

All offers in

Format Conversion IP

Filter

Compare

5

Format Conversion IP

from

4

vendors

(1

-

5)

-

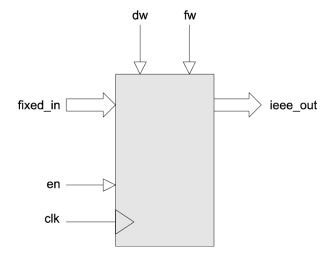

Fixed-point to 32-bit floating-point converter

- Converts fixed-point numbers to 32-bit floating-point representation. The fixed-point input has a configurable word and fraction width.

- Floating-point outputs are based on the IEEE 754 standard.

- The design features a high-speed, fully pipelined architecture with a 2 clock-cycle latency.

-

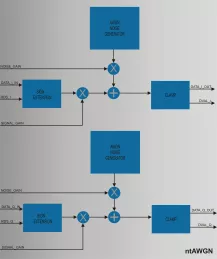

Additive White Gaussian Noise Generator

- High precision AWGN Channel emulator.

- Programmable Pseudo Random Generator(LFSR).

- Programmable number of output bits.

-

Single precision, IEEE 754, integer to floating point conversion

- Single-precision (32-bit) integer to floating point conversion.

- IEEE 754 compliant.

- Support for signed and unsigned integers.

- Status flags indicating invalid.

-

Single precision, IEEE 754, floating point to integer conversion

- Single-precision (32-bit) floating point to integer conversion.

- IEEE 754 compliant.

- Support for signed and unsigned integers.

- Full support for infinities, NaNs and denormals.

-

Color Camera Sensor Bayer Decoder

- Converts Bayer image into the RGB image

- Supports all Bayer pattern combinations

- Optional built-in LVDS receiver compatible with the Micron MT9V022 automotive sensor

- Unlimited vertical pixel resolution