The AMBA5 CHI Verification IP provides an effective & efficient way to verify the components interfacing with AMBA 5 CHI bus of an IP or SoC. The AMBA5 CHI VIP is fully compliant with standard AMBA5 CHI specifications from ARM. This VIP is a lightweight VIP with an easy plug-and-play interface so that there is no hit on the design cycle time.

AMBA 5 CHI Verification IP

Overview

Key Features

- VIP is Compliant with the latest ARM™ AMBA5 CHI.

- Support any type of network topology like Crossbar, Ring, Mesh, etc…

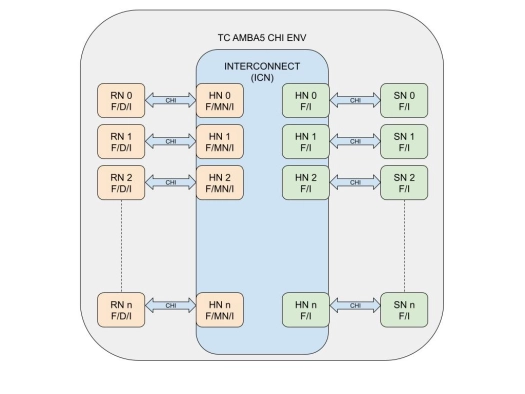

- Support for all types of AMBA5 CHI Nodes:

- Requester (RN-F, RN-D, RN-I)

- Home (HN-F, HN-I)

- Subordinate (SN-F, SN-I)

- Support DMT, DWT, and DCT.

- Support all types of transaction identifiers

- GUI for easy analyzing packet debugging and decoding

- All types of protocol, and link layer attributes are visible in packet & flit format.

- Strong protocol checking Bus Monitor which also provides statistics ofthe transactions

- Parameterized Flit data

- All types of ordering modes, Request Retry are supported

- Each cache line states , Request type, Response type, Snoop request & snoop response are supported

- Exclusive, Cache stashing

- DVM operation with address translation supported

- Support REM features

- Support Memory tagging, MPAM, PBHA.

- Support Persistent and deep Persistent

- Support Link activation & deactivation, protocol layer activation & deactivation.

- Support Requester coherency request & acknowledge.

- Support data poison & check_type

- Support Critical chunk first wrap order

Block Diagram