MIPI Controller IP

MIPI Controller IP cores manage the flow of data between processors and peripherals, ensuring seamless integration and low-power operation. MIPI Controller IP supports a wide range of MIPI interfaces, such as MIPI CSI-2 IP for camera modules, MIPI DSI IP for display applications, and MIPI UFS IP for storage solutions. Additionally, other MIPI interfaces like MIPI I3C IP, MIPI SLIMbus IP, and MIPI SoundWire IP offer flexible solutions for sensor, audio, and bus communication.

All offers in

MIPI Controller IP

Filter

Compare

377

MIPI Controller IP

from 34 vendors

(1

-

10)

-

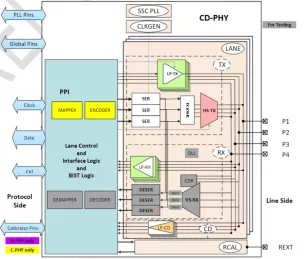

MIPI C-PHY/D-PHY Combo CSI-2 RX+ IP (6.0Gsps/trio, 4.5Gbps/lane) in TSMC N6

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

-

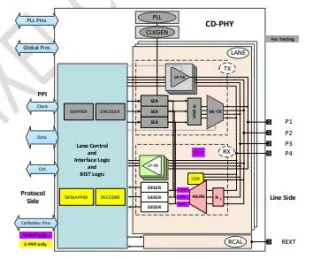

MIPI C-PHY/D-PHY Combo RX+ IP 4.5Gsps/4.5Gbps in TSMC N5

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

-

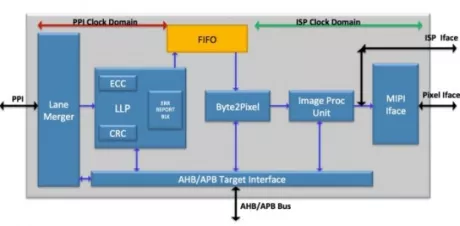

MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

-

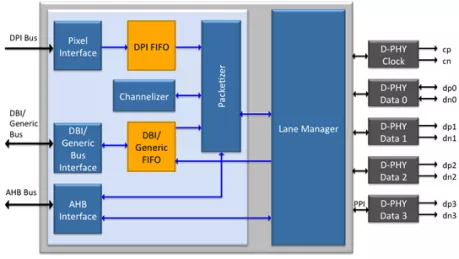

MIPI DSI Transmit Controller v1.3

- Compliant with the following MIPI specifications

- DSI Host-side (display module) interface supports

- Application Processor Connectivity and video/command processing

- AHB Interface for register configuration and monitoring using programmed IO

-

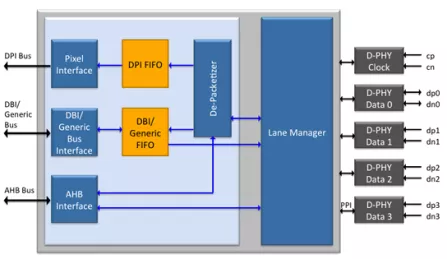

MIPI DSI Receiver Controller v1.3

- Compliant with the following MIPI specifications

- DSI Host-side interface supports

- Display Panel Connectivity and video/command processing

-

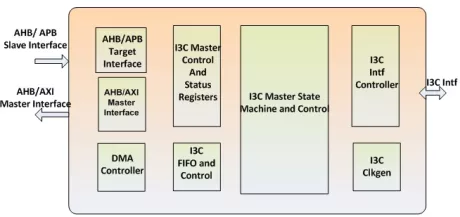

I3C Host Controller

- Compliant with MIPI I3C Specification V1.0

- Supports up to 12.5 MHz operation using Push-Pull.

-

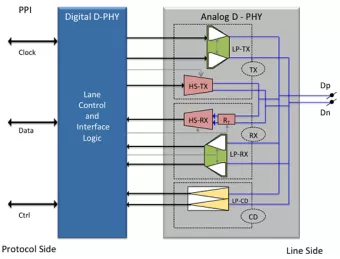

MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- Compliant to MIPI Alliance Standard for D-PHY specification Version 2.1, 1.2, 1.1

- Supports standard PHY transceiver compliant to MIPI Specification

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high speed mode with a bit rate of 80-2500 Mb/s

-

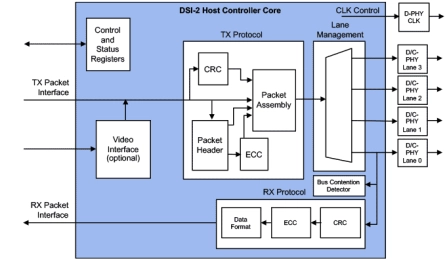

MIPI DSI-2 Controller Core

- Fully MIPI DSI-2/DSI standard compliant

- 64 and 32-bit core widths

- Host (Tx) and Peripheral (Rx) versions

- Supports 1-4, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

- Supports all data types

-

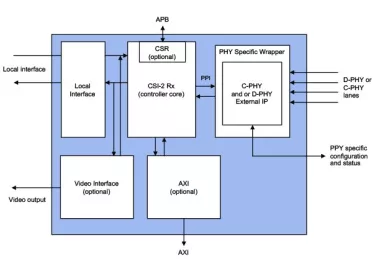

MIPI CSI-2 Controller Core

- Fully MIPI CSI-2 standard compliant

- 64 and 32-bit core widths

- Transmit and Receive versions

- Supports 1-8, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

- Supports all data types

-

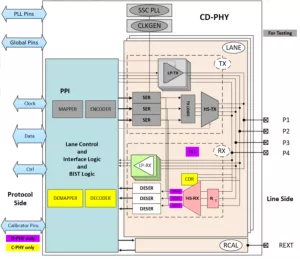

MIPI C-PHY/D-PHY Combo TX+ IP 4.5Gsps/4.5Gbps in TSMC N5

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode