MIPI CSI-3 IP

As part of the MIPI (Mobile Industry Processor Interface) standard, MIPI CSI-3 IP offers significant improvements over previous generations, providing faster data rates and enhanced performance for imaging applications. Ideal for next-generation cameras, sensors, and imaging systems, MIPI CSI-3 IP supports multiple lanes for efficient data transfer, ensuring superior image quality and low power consumption.

All offers in

MIPI CSI-3 IP

Filter

Compare

23

MIPI CSI-3 IP

from 4 vendors

(1

-

10)

-

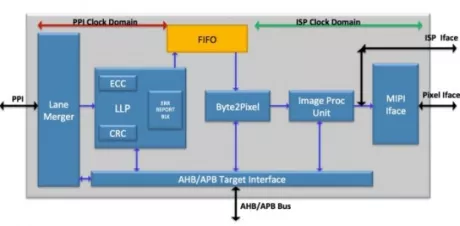

MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

-

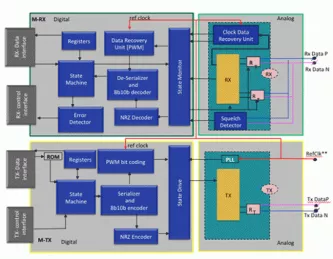

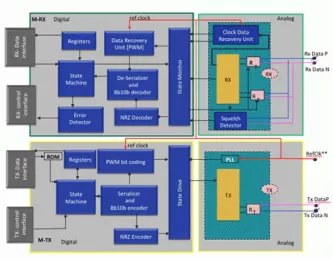

MIPI M-PHY G4 Designed For TSMC 28nm HPC+

- Compliant to MIPI Alliance Standard for M-PHY specification Version 4.1

- Supports M-PHY Type-I system

- Support for Clock and Data Recovery Options

-

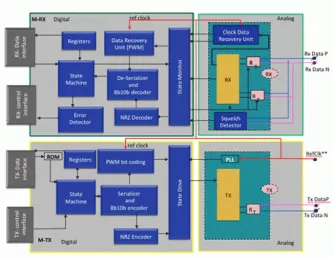

MIPI M-PHY - TSMC 40nm

- Compliant to MIPI Alliance Standard for M-PHY specification Version 3.0

- •Supports high speed data transfer G1A/B, G2A/B and G3A/B with data rates of up to 5830.4 Mbps

- •Supports M-PHY Type-I system

- •Support for reference clock frequencies of 19.2MHz/26MHz/38.4MHz/52MHz

-

MIPI M-PHY Designed For GF 28nm

- •Compliant to MIPI Alliance Standard for M-PHY specification Version 3.0

- •Supports high speed data transfer G1A/B, G2A/B and G3A/B with data rates of up to 5830.4 Mbps

- •Supports M-PHY Type-I system

- •Support for reference clock frequencies of 19.2MHz/26MHz/38.4MHz/52MHz

-

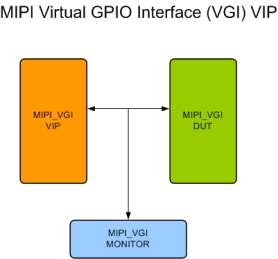

MIPI VGI Verification IP

- Compliant to version 0.9 of Draft MIPI VGI specifications.

- Full MIPI VGI Host and Peripheral functionality.

- Supports Point to Point, Full duplex communication.

- Supports 2-wire Asynchronous and 3-wire Synchronous interface.

-

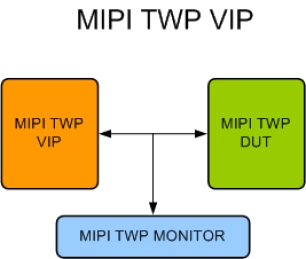

MIPI TWP Verification IP

- Compliant with MIPI TWP Specification version 1.1.

- Supports ATB interface.

- Supports allows up to 111 source trace streams to be represented as a single stream and later separated by either hardware or software.

- Supports require low additional bandwidth.

-

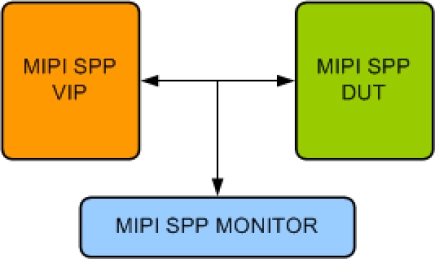

MIPI SPP Verification IP

- Supports version 2.0 Specification.

- Full MIPI SPP Debug Test System (Master) and Target System (Slave) functionality.

- Supports Independent, Full-Duplex Communication.

- Supports dynamic sizing of SPTBs with following types.

-

MIPI HTI Verification IP

- Supports MIPI HTI version 1.0 and 1.1 specification.

- Supports Point-to-point topology

- Supports multiple lanes up to 8 lanes.

- Supports NRZ line encoding.

-

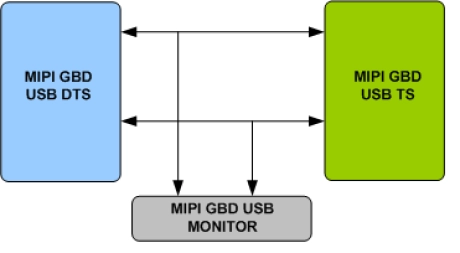

MIPI GbD USB Verification IP

- Compliant with MIPI Giga bit debug specification version 1.0/1.1

- Supports the network adaptor for USB

- Supports the trace applications

- Supports the Sneak peak applications

-

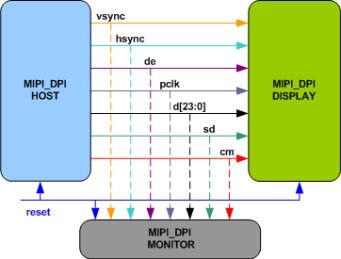

MIPI DPI Verification IP

- Supports 2.0 MIPI DPI Specifications.

- Supports Type 2, Type 3 and Type 4 Architecture.

- Supports programming display parameters

- Error Injection