MIPI DigRF v4 IP

MIPI DigRF v4 IP (Digital Radio Frequency Interface Version 4) is a high-speed interface IP that is used to interconnect the RFIC in a device with the baseband processor. It is designed to provide a convenient approach for integrating components and meeting the data-intensive needs of 4G LTE air interfaces that require high channel bandwidth.

All offers in

MIPI DigRF v4 IP

Filter

Compare

7

MIPI DigRF v4 IP

from 2 vendors

(1

-

7)

-

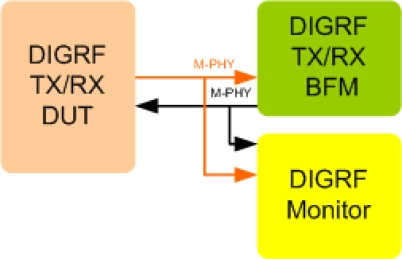

MIPI DigRF Verification IP

- Supports 1.2 MIPI DIGRF Specification.

- Supports both Data and Control frames

- Supports frames nesting

- Supports up to four lanes

-

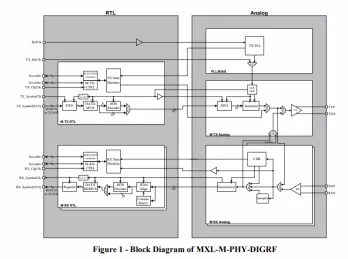

MIPI M-PHY in TSMC 65LP

- Supports the MIPI Standard for M-PHY, Draft Specification v0.90.00-r02 and DigRF v4 V1.10.00.0.04

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports HS mode (GEAR 1-2, A & B)

-

MIPI M-PHY in SMIC 90LL

- Supports MIPI Standard for M-PHY v3.0.

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

-

MIPI M-PHY in SMIC 130nm

- Complies with MIPI Standard for M-PHY v3.0

- Slew-rate control for EMI reduction

- Supports HS modes GEAR 1-3

-

MIPI M-PHY (HS-G3) in GF 28LP

- Complies with MIPI Standard for M-PHY v3.0

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

-

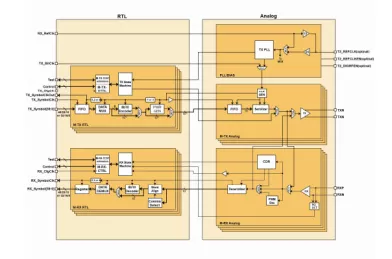

MIPI M-PHY DigRF Compliant IP

- Complies with MIPI Standard for M-PHY, Draft Specification v0.90.00- r02 and DigRF v4 V1.10.00.0.04

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports HS mode (GEAR 1-2, A & B)

-

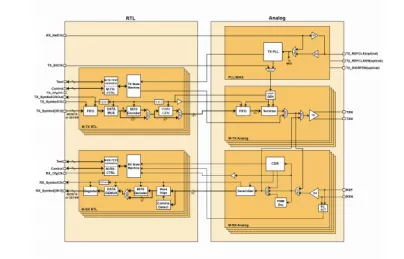

MIPI M-PHY Compliant (HS-G2) IP

- Complies with MIPI Standard for M-PHY, Draft Specification v0.90.

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports all HS modes (GEAR 1-2)