MIPI DigRF 3G IP

The MIPI DigRF v3 IP is a low-power, low pin-count serial interface that simplifies the integration and interoperability between the RF transceiver IC and baseband IC (BBIC). The six-pin digital interconnect reduces system cost and lowers Electromagnetic Interference (EMI) for dual and single-mode 3GPP 2.5/3G mobile terminals. With a maximum throughput of 312Mbps, the interface uses a simple frame based protocol applicable to 2.5G GPRS/EGPRS and release 5, 6 and 7 FDD UMTS including HSDPA, HSUPA with Rx diversity.

All offers in

MIPI DigRF 3G IP

Filter

Compare

20

MIPI DigRF 3G IP

from 2 vendors

(1

-

10)

-

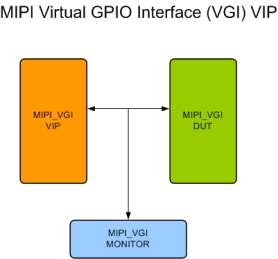

MIPI VGI Verification IP

- Compliant to version 0.9 of Draft MIPI VGI specifications.

- Full MIPI VGI Host and Peripheral functionality.

- Supports Point to Point, Full duplex communication.

- Supports 2-wire Asynchronous and 3-wire Synchronous interface.

-

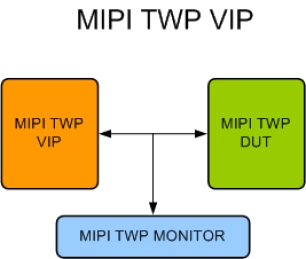

MIPI TWP Verification IP

- Compliant with MIPI TWP Specification version 1.1.

- Supports ATB interface.

- Supports allows up to 111 source trace streams to be represented as a single stream and later separated by either hardware or software.

- Supports require low additional bandwidth.

-

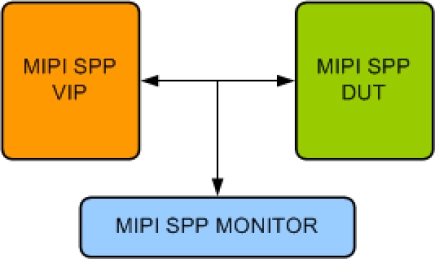

MIPI SPP Verification IP

- Supports version 2.0 Specification.

- Full MIPI SPP Debug Test System (Master) and Target System (Slave) functionality.

- Supports Independent, Full-Duplex Communication.

- Supports dynamic sizing of SPTBs with following types.

-

MIPI HTI Verification IP

- Supports MIPI HTI version 1.0 and 1.1 specification.

- Supports Point-to-point topology

- Supports multiple lanes up to 8 lanes.

- Supports NRZ line encoding.

-

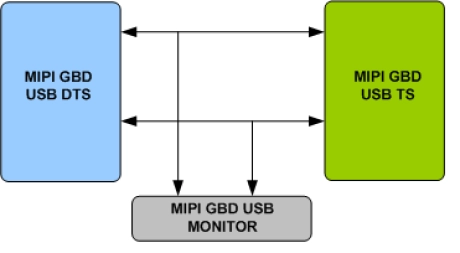

MIPI GbD USB Verification IP

- Compliant with MIPI Giga bit debug specification version 1.0/1.1

- Supports the network adaptor for USB

- Supports the trace applications

- Supports the Sneak peak applications

-

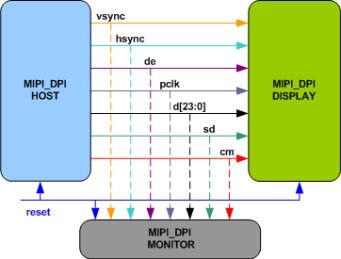

MIPI DPI Verification IP

- Supports 2.0 MIPI DPI Specifications.

- Supports Type 2, Type 3 and Type 4 Architecture.

- Supports programming display parameters

- Error Injection

-

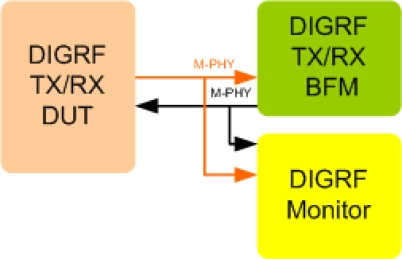

MIPI DigRF Verification IP

- Supports 1.2 MIPI DIGRF Specification.

- Supports both Data and Control frames

- Supports frames nesting

- Supports up to four lanes

-

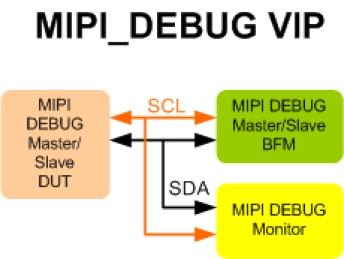

MIPI DEBUG Verification IP

- Compliant with MIPI Debug version 1.0 specification.

- Full MIPI Debug functionality.

- Support full I3C Slave with CCC, Hot Join, IBI, DAA and HDR mode.

- Full Link and Network/Transport layer.

-

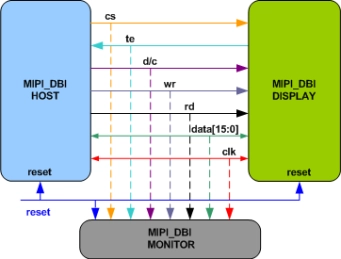

MIPI DBI Verification IP

- Compliant to MIPI DBI v2.0 Specification.

- Supports Type A, Type B and Type C Interfaces.

- Supports Type 1, Type 2 and Type 3 Architecture.

- Supports all types of Display Command Set types

-

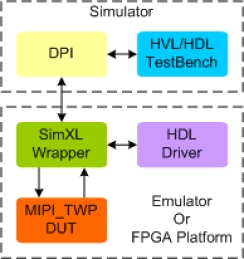

MIPI TWP Synthesizable Transactor

- Compliant with MIPI TWP version 2.0 specification.

- Full MIPI Debug functionality.

- Supports all Debug CCC's and Opcodes

- Supports following three layer