Interconnect IP for GLOBALFOUNDRIES

Welcome to the ultimate Interconnect IP for GLOBALFOUNDRIES hub! Explore our vast directory of Interconnect IP for GLOBALFOUNDRIES

All offers in

Interconnect IP

for GLOBALFOUNDRIES

Filter

Compare

168

Interconnect IP

for GLOBALFOUNDRIES

from 25 vendors

(1

-

10)

-

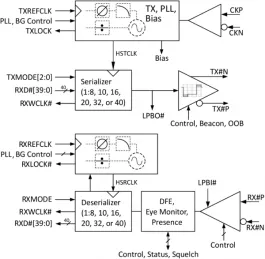

Multiprotocol SerDes PMA

- Supports over 30 protocols including CEI 6G & 11G SR, MR, LR, Ethernet 10GBASE-X/S/K/R, PCIe Gen1/2/3/4, V-by-One HS/US, CPRI, PON, OTN/OTU, 3GSDI, JESD204A/B/C, SATA1-3, XAUI, SGMII

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, or 40 bit

- Tx ring PLL includes fractional multiplication, spread spectrum and Jitter Cleaner function for Sync-E and OTU

- Core-voltage line driver with programmable pre-and post-emphasis

-

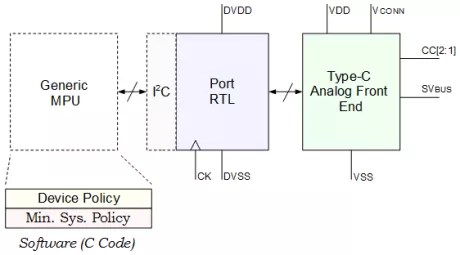

Complete USB Type-C Power Delivery IP

- Mixed signal Analog Front End Macros for 65n, 130n, 150nm, and 180n technologies.

- RTL code from AFE to I2C compatible register set.

- Stand alone C code for Protocol, Device Policy Manager, and System Policy Manager.

- IP demonstration & development board, with compliance reports.

- Full chip integration of USB Type-C, and associated software.

-

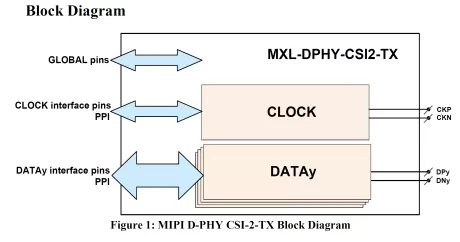

MIPI D-PHY CSI-2 TX (Transmitter) in GlobalFoundries 22FDX

- Consists of 1 Clock lane and up to 4 Data lanes

- Supports MIPI Alliance Specification for D-PHY Version 2.1

-

MIPI DPHY Receiver on GF55LPe

- MIPI D-PHY version 1.2 compliant PHY receiver

- Consists of 4 data lane and 1 clock lane

-

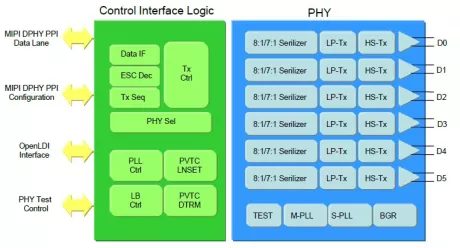

MIPI DPHY & LVDS Transmit Combo on GF55LPe

- MIPI D-PHY version 1.2 compliant PHY transmitter

- OpenLDI version 0.9 compliant LVDS transmitter

-

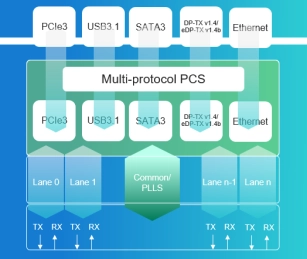

PHY for PCIe 3.1

- Supports PCIe 3.1, USB 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

- Supports internal and external clock sources with clock active detection

-

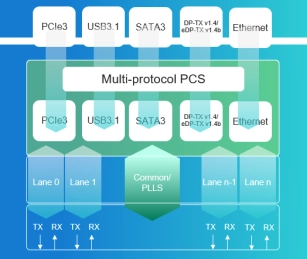

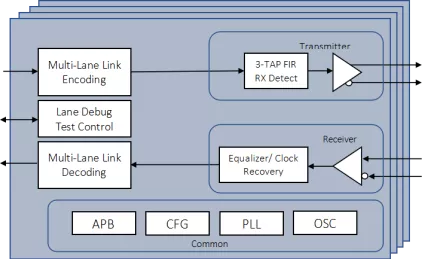

Ethernet SerDes - 16Gbps and 10Gbps multi-protocol SerDes PHY

- Wide range of protocols that support networking, HPC, and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- Extensive set of isolation, test modes, and loop-backs including APB and JTAG

- Supports 16-bit, 20-bit, and 32-bit PIPE and non-PIPE interfaces

- Selectable serial pin polarity reversal for both transmit and receive paths

-

PCIe Gen2 PHY

- PCI Express Gen 2 and Gen 1 compliant

- Supports various PCI Express modes and extensions

- Programmable amplitude and pre-emphasis

- Programmable receiver equalization

-

PCIe Gen3 PHY

- Low Risk - Silicon proven with Si characterization data

- Excellent Interoperability

- Superior Noise Immunity

-

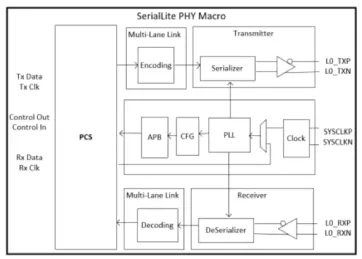

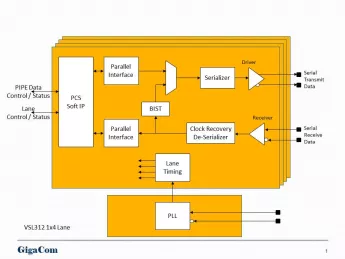

SerialLite PHY with PCS

- Integrated PCS Layer

- Low power & area

- Test Silicon