The VSG1G55SL2 is an enhanced High-Speed SerialLite macro with data transfer capabilities of up-to 3.125Gbps. It includes the PCS layer within the Macro and is capable of directly interfacing with the ASIC core. In addition, on the same footprint using Gigacom's technology, it includes a standard JTAG interface, Scan interface and a Serial interface.

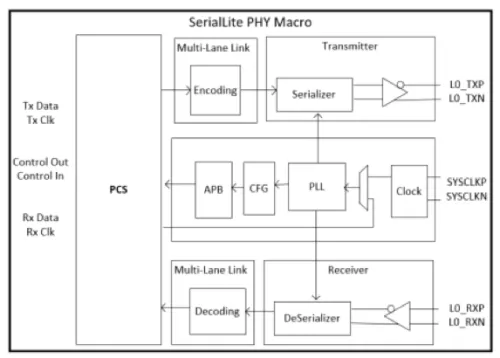

SerialLite PHY with PCS

Overview

Key Features

- Standards Compliance

- SerialLite

- 8b/10b encoding

- IEEE 1149.1

- High-Speed Data Transfer

- Up-to 3.125Gbps per lane

- Up-to 8 lanes, for a combined total of 50Gbps

- Low Power

- Automatic shut-off when not enabled ensures minimum power consumption

- Protocol features

- Streaming or packet-based protocols

- Nesting for time-critical control packet

- Lane polarity reversal

- Error detection

- Packet retransmit on error for priority packets

- On-Chip IO ring compatibility

- Designed as an IO-ring component

- Small footprint

- Wire-Bond and Flip-Chip compatible

- Clocking

- Flexible clocking options, including internal and external, direct or crystal-based

- Optional Features

- JTAG Interface

- Embedded TAP controller

- Extensive Test and Debug Features

- Scan

- DC JTAG

- Serial Debug Access

- Configurability

- Programmable lane enable/disable

- Choice of macros pre-configured for 1 to 8 lanes

Benefits

- Integrated PCS Layer

- Low power & area

- Test Silicon

- Integration support

- Customization based on customer requirement

Block Diagram

Applications

- Standard SerialLite Specification

- Packet or streaming data applications for chip2chip, board2board, shelf2shelf or backplane

- High-Speed Debug/Test data transfer

- Real-Time monitoring of on-chip signals/bus

- Silicon Debug

Deliverables

- Complete set of logical views, physical views, and documentation, including a Verilog model, a UVM-based verification environment, abstract view, liberty files, GDS-II and netlist

Technical Specifications

Foundry, Node

GlobalFoundries 55nm

Maturity

Test Silicon

Availability

Immediately

GLOBALFOUNDRIES

Pre-Silicon:

55nm