USB 3.1 IP

Welcome to the ultimate USB 3.1 IP hub! Explore our vast directory of USB 3.1 IP

All offers in

USB 3.1 IP

Filter

Compare

85

USB 3.1 IP

from 10 vendors

(1

-

10)

-

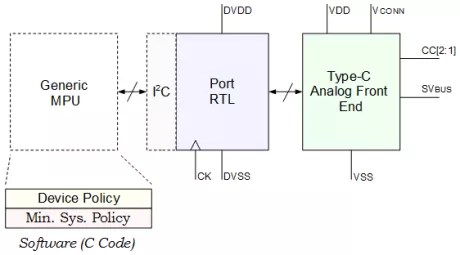

Complete USB Type-C Power Delivery IP

- Mixed signal Analog Front End Macros for 65n, 130n, 150nm, and 180n technologies.

- RTL code from AFE to I2C compatible register set.

- Stand alone C code for Protocol, Device Policy Manager, and System Policy Manager.

- IP demonstration & development board, with compliance reports.

- Full chip integration of USB Type-C, and associated software.

-

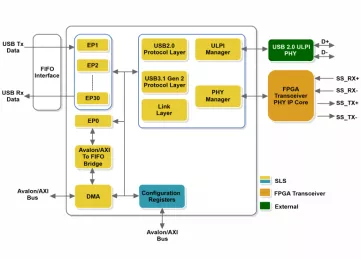

eUSB 3.1 Gen 2 Device Controller - Software Enumeration, FIFO Interface

- Software Enumeration

- FIFO Interface

-

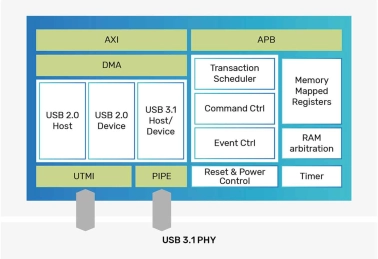

USB 3.x Controller

- Full Link Power Management (U0, U1, U2, and U3) with LFPS support

- Up to 15 IN and 15 OUT configurable endpoints

- Power and clock gating feature support

- Multi-channel Scatter/Gather DMA with TRB caching

- AXI features 128-bit datapath width and 64-bit address width

-

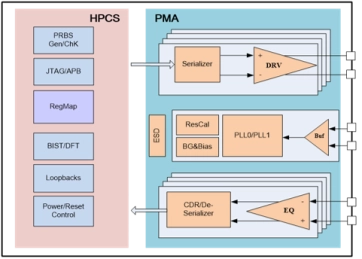

USB3.1 transceiver IP with PMA and PCS layer

- Data rate for Gen 1 physical layer is 5Gbps

- Data rate for Gen 2 physical layer is 10Gbps

- 4 Channel per Quad

- Shared high performance LC tank PLL

-

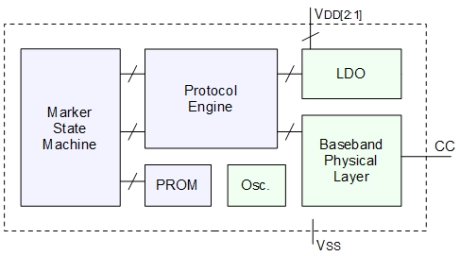

USB 3.1 Cable Marker IP

- The OTC9115 is a complete, low cost, single chip cable marker for USB PD Type-C (baseband) cables.

- In low silicon area and just 4 IOs, the device has been designed exclusively for very high volume Type-C cables with basic marker requirements.

-

USB 3.1 Host Premium

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Configurable data buffering options to optimize performance vs area

- Lowers overall system power by design

- Supports SuperSpeed and High-Speed modes

-

USB 3.1 DRD Premium

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Configurable data buffering options to optimize performance vs area

- Lowers overall system power by design

- Supports SuperSpeed and High-Speed modes

-

SuperSpeed USB 3.1 Host Controller Multiport

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Configurable data buffering options to optimize performance vs area

- Lowers overall system power by design

- Supports SuperSpeed and High-Speed modes

-

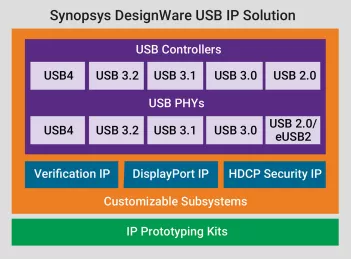

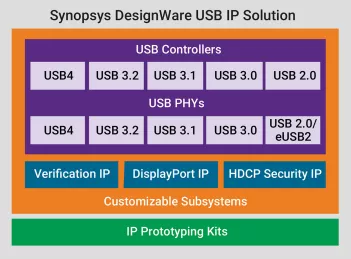

USB-C 3.1/DP TX PHY for TSMC N7, North/South Poly Orientation for Automotive AEC-Q100 Grade 2

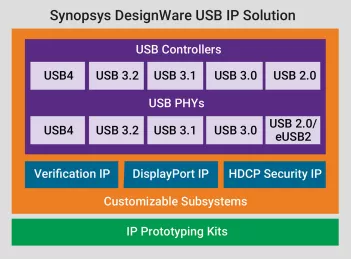

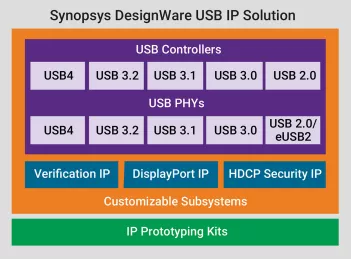

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB-C 3.1 SS/SSP PHY, Type-C - TSMC N5A 1.2V, North/South Poly Orientation for Automotive AEC-Q100 Grade 2

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes