Ethernet PHY IP

Welcome to the ultimate Ethernet PHY IP hub! Explore our vast directory of Ethernet PHY IP

The Ethernet PHY IP cores encode data frames for transmission and decode received frames with a specific modulation speed of operation, transmission media type and supported link length.

All offers in

Ethernet PHY IP

Filter

Compare

69

Ethernet PHY IP

from 13 vendors

(1

-

10)

-

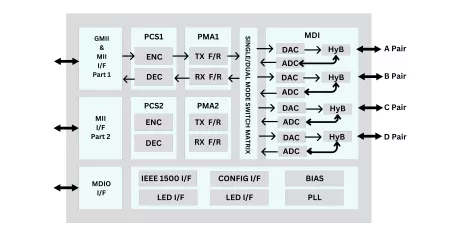

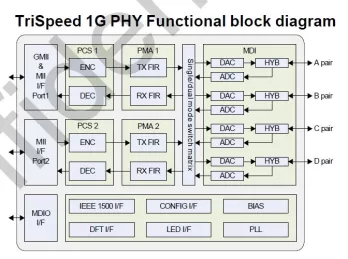

Silicon Proven 1G Ethernet PHY IP as Whitebox

- IEEE 802.3-2008, IEEE 802.3az fully standards compliant

- IEEE 1588-2008 support

- BroadR-Reach™ support

- Dual port MAC interface:

-

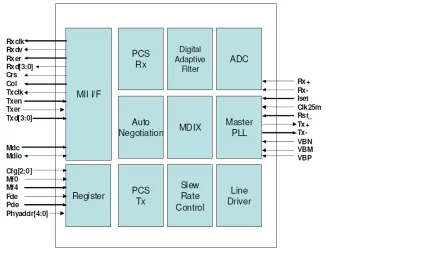

Ethernet 10/100 PHY

- Supports MII.

- Auto-MDX

- 10/100Mbs operation supported

- Full/half duplex operation

-

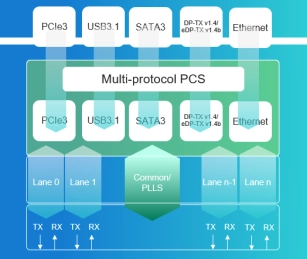

Ethernet SerDes - 16Gbps and 10Gbps multi-protocol SerDes PHY

- Wide range of protocols that support networking, HPC, and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- Extensive set of isolation, test modes, and loop-backs including APB and JTAG

- Supports 16-bit, 20-bit, and 32-bit PIPE and non-PIPE interfaces

- Selectable serial pin polarity reversal for both transmit and receive paths

-

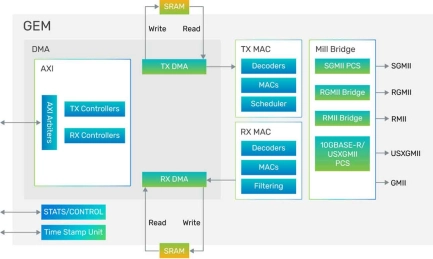

Ethernet PCS IP - Integrates MAC IP to a broad range of PHY and SerDes IP

- Mature: Silicon-proven design in volume production at multiple customers

- Ease-of-use: Customizable with easy integration

- Designed by an Industry Leader: Cadence is an active contributor to the IEEE 802.3 standards working groups

-

10/100/1000 base T ethernet Phy

- IEEE 802.3-2008, IEEE 802.3az fully standards compliant

- IEEE 1588-2008 support

- BroadR-Reach™ support

- Dual port MAC interface:

-

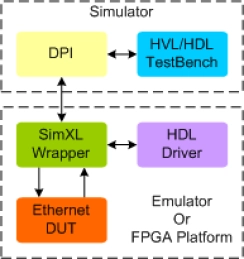

Ethernet Synthesizable Transactor

- Supports Full MII/RMII/SMII TX/RX functionality

- Supports Mac control and data frames support

- Ability to generate VLAN tagged and Priority tagged frames

- Supports Pause frame detection and generation

-

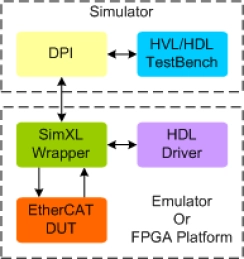

Ethercat Synthesizable Transactor

- Supports ETG.1000 S(R) V1.0.3 specification

- Supports Low Voltage Differential signaling interface

- Supports MII, MDIO RMII and RGMII Interface as per the ISO/IEC 8802-3 specification

- Supports RMII and RGMII Interface

-

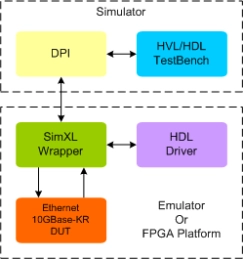

Ethernet 10GBase-KR Synthesizable Transactor

- Supports 10G as per 802.3:

- Supports XGMII

- Supports XTBI (i.e Output of 8b/10b PCS)

- Supports 10GBASE-KR with scrambler

-

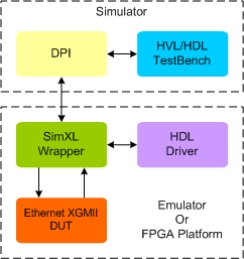

Ethernet XGMII Synthesizable Transactor

- Follows XGMII specification as defined in IEEE 802.3

- Supports Mac control and data frames support

- Ability to generate VLAN tagged and Priority tagged frames

- Supports Pause frame detection and generation

-

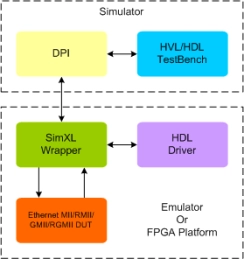

Ethernet MII/RMII/GMII/RGMII Synthesizable Transactor

- Supports Full MII/RMII/GMII/RGMII TX/RX functionality

- Supports Mac control and data frames support

- Ability to generate VLAN tagged and Priority tagged frames

- Supports Pause frame detection and generation