SATA IP

Welcome to the ultimate SATA IP hub! Explore our vast directory of SATA IP cores.

SATA-IP IP cores are designed to handle SATA Protocol and communicate with SATA compliant device without need CPU/OS and External DDR memory. SATA storage is suitable for low cost and large storage capacity with easily scalable SATA Channel to support RAID system.

All offers in

SATA IP

Filter

Compare

102

SATA IP

from 28 vendors

(1

-

10)

-

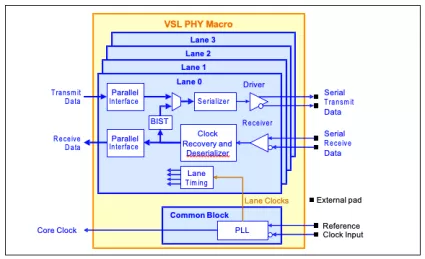

SATA 3 PHY

- Serial ATA III Revision 3.3 compliant

- Gen1i, Gen1m, Gen2i, Gen2m compliant

- Gen1x, Gen2x compatible

-

Serial ATA I/II/III Host Controller IP Core Compliance Certified by UNH Labs

- High Throughput

- Low Latency

- Connects to SAPIS compliant serial ATA Phy

-

SATA PHY

- Serial ATA II Revision 2.6 compliant

- Gen1i, Gen1m, Gen2i, Gen2m compliant

- Gen1x, Gen2x compatible

- Initialization and power saving modes

-

Serial ATA I/II Device Controller IP Core

- The Serial ATA Device Controller IP Core provides an interface to high-speed serial link replacements for the parallel ATA attachment of mass storage devices.

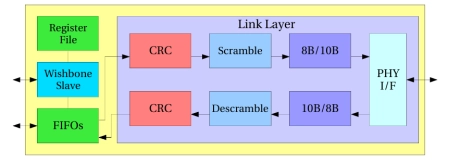

- The serial link employed is a high-speed differential layer that utilizes Gigabit technology and 8b/10b encoding.

-

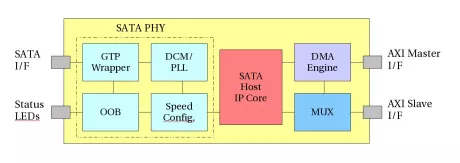

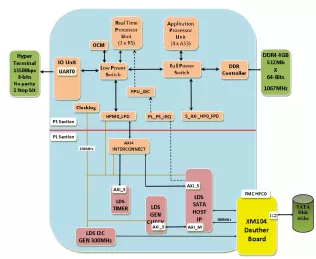

Xilinx Ultra Scale Plus SATA HOST IP

- Compliant with Serial ATA III specification and signaling rate is 6Gbs

- Xilinx Ultra Scale Plus GTHE4 FPGA

-

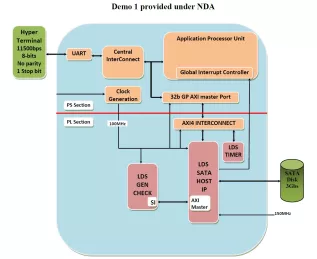

SATA Host on Xilinx Zynq Artix 7

- Compliant with Serial ATA III specification

- Signaling rate: 6Gbs

- Fully synchronous

-

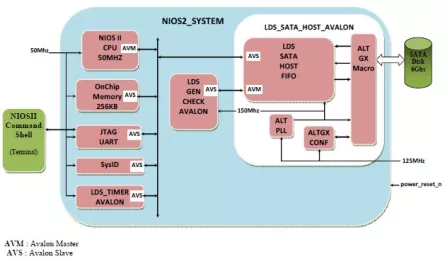

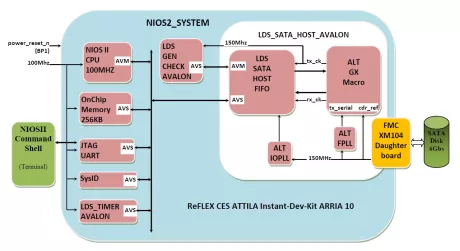

SATA 3 HOST IP on ARRIA 10 FPGA

- Rate Match FIFO

- - Manage SATA reference frequency difference between the FPGA and the Disk

- Physical Layer features

- - Detect OOB and COMWAKE

-

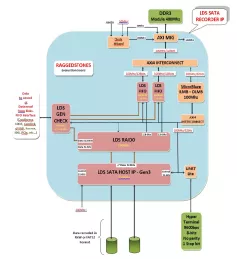

LDS SATA RECORDER IP ON ARTIX 7

- The LDS SATA RECORDER XA7 IP is a complete recorder sub-system IP. It can be configured according to the recording performance required and the quantity of the data to be recorded.

- - The data can be recorded in FAT32 or in RAW format.

- - The Ethernet link, when used, enables to download FAT32 files into your PC to process them later according to user application (It is not intended to record data, but it can do).

- o 1Gbits LDS Mac in GMII or 10Gbits Ethernet LDS Mac with XGMII or XAUI interface.

-

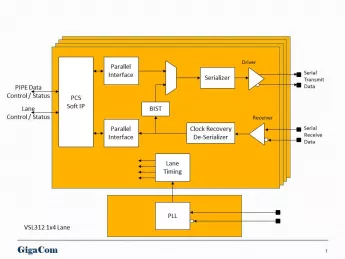

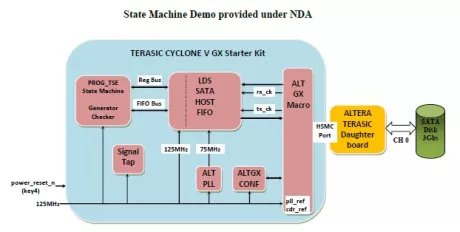

SATA 2 HOST ON CYCLONE 5 GX

- Compliant with Serial ATA II specifications

- Fixed Speed 3Gbs or 1.5Gbs

-

SATA 3 Host Controller on ARRIA V FPGA

- Compliant with Serial ATA III specification and signaling rate is 6Gbps and scalable 3Gbs

- Fully synchronous