DDR5 Controller IP

Welcome to the ultimate DDR5 Controller IP hub! Explore our vast directory of DDR5 Controller IP

All offers in

DDR5 Controller IP

Filter

Compare

46

DDR5 Controller IP

from 13 vendors

(1

-

10)

-

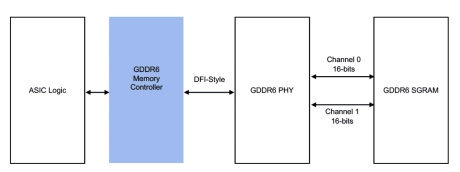

GDDR6 Controller

- Supports up to 24 Gb/s per pin operation

- Can handle two x16 GDDR6 channels with one controller or independently with two controllers

- Supports x8 or x16 clamshell mode

- Queue-based interface optimizes performance and throughput

- Maximizes memory bandwidth and minimizes latency via Look-Ahead command processing

- Automatic retry on transactions where EDC error detected

-

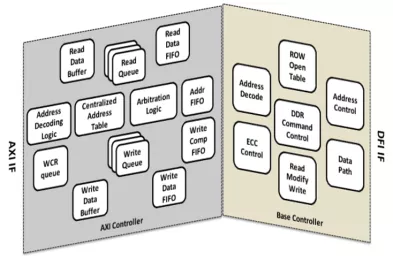

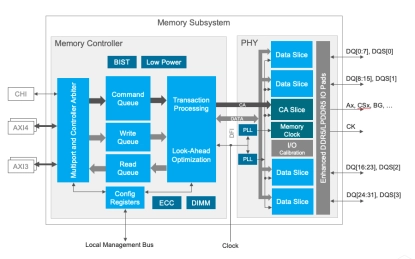

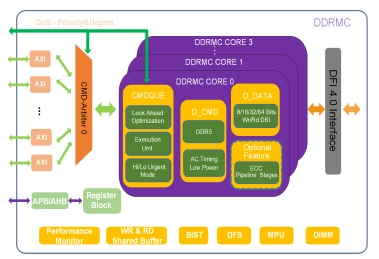

High Performance DDR5/4/3 Memory Controller

- Compliant with AXI4 Specification

- Compliant with DFI 3.1 Specification

- Compliant with JEDEC DDR3, DDR3L, DDR4 and DDR5 standards

- Supports 64, 32, 16 and 8 bit Memory SDRAM for DDR3L, DDR4 and DDR5

-

GDDR6 Memory Controller IP

- JEDEC GDDR6 standard JESD250B

- Fast frequency switching

- Flexible Configuration

-

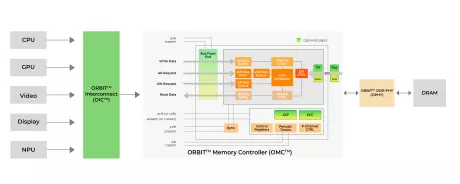

DDR/LPDDR Controller

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 and DDR5/4/3 protocol memories

- Memory controller interface complies with DFI standards up to version 5.0

- Priority per command on Arm® AMBA® 4 AXI, AMBA 3 AXI

-

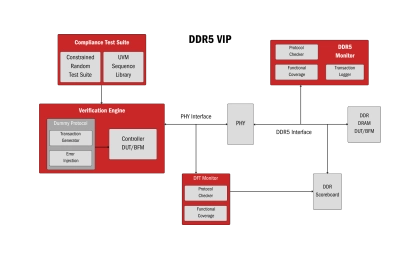

DDR5 Controller - Ensures high-speed, efficient operation and compatibility of memory controllers

- DDR5 Verification IP supports data rates up to 8400 MT/s, ensuring high-performance memory controllers meet the latest standards for speed, capacity, and power efficiency. It is designed to validate advanced features such as error correction and power management.

- This tool is ideal for validating DDR5 controllers in applications ranging from high-performance computing to mobile devices, ensuring robust performance and seamless integration in various systems

-

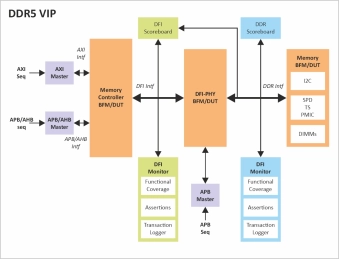

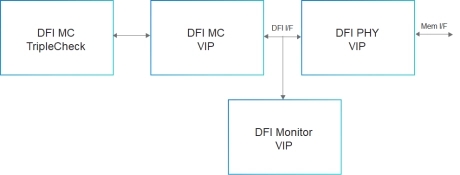

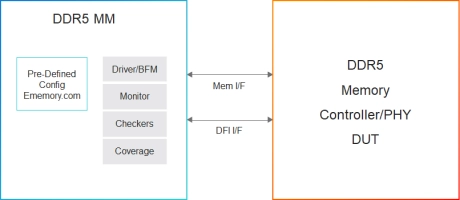

Simulation VIP for DFI

- DFI MC

- Command Interface

- Drives Command on different phases based on memory protocol requirement

- DDR4-5, LPDDR4-5, HBM2E-3 and GDDR6-7

-

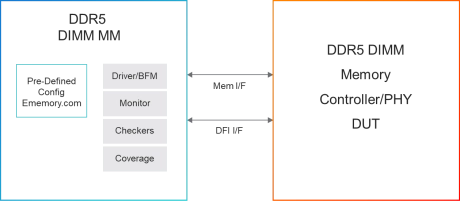

Simulation VIP for DDR5 DIMM

- DIMM Types

- DDR5 UDIMM, RDIMM, and LRDIMM

- Size

- 32Gb, 64Gb, and 128Gb

-

Simulation VIP for DDR5

- Speeds

- 3200, 3600, 4000, 4400, 4800, 5200, 5600, 6000, and 6400

- Density

- 8Gb, 16Gb, 24Gb, 32Gb, and 64Gb

-

DDR5 IP solution

- Compatible with DDR5 up to 4800Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI5.0/4.0 compliant interface between controller and PHY

- Support ECC (error correcting code)

-

DDR5 RDIMM Verification IP

- The DDR5 RDIMM Verification IP provides an effective & efficient way to verify the components interfacing with DDR5 RDIMM interface of an ASIC/FPGA or SoC.

- The DDR5 RDIMM VIP is fully compliant with Standard DDR5 specification from JEDEC.

- This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.