OPENEDGES, the memory system IP provider, including DDR memory controller, DDR PHY, on-chip interconnect, and NPU IP together as an integrated solution or independent IP. They are tightly combined to bring synergy for high performance and low latency. OPENEDGES' integrated IP solutions are market and silicon-proven, featuring advanced architectures and proprietary technologies that enable customers to shorten their design and verification processes.

OMC – GDDR6 Memory Controller is a small & highly configurable IP. It provides high performance through advanced memory controller design based on a proprietary out-of-order scheduling algorithm and high-speed implementation technique. Demand for more DRAM bandwidth is getting stronger than ever in a quest to improve user experiences (e.g., higher image resolution). Given the limited amount of physically available DRAM bandwidth, highly efficient memory controller IP is becoming a very critical issue everywhere. With our OMC – GDDR6 Memory Controller, SoCs can save a significant amount of area & power consumption and meet next-generation SoC’s DRAM bandwidth requirements.

GDDR6 Memory Controller IP

Overview

Key Features

- JEDEC GDDR6 standard JESD250B

- Data rates up to +18 Gbps/s/pin

- Capacity from 8Gb to 32Gb

- Fast frequency switching

- Full automated HW sequence

- Flexible Configuration

- Two OMCs drive each 16x channels

- One OMC drives two 16x channels (lock-step)

- Highly flexible & configurable

- Interface

- AXI4, APB4 Interface to bus

- DFI Interface to PHY

- 1:2 DFI freq. ratio

- EDC signals added to DFI 4.0 for GDDR6

Benefits

- High Utilization

- Over 90% DRAM utilization over real-life memory access traces through proprietary out-of-order scheduling algorithm

- Highly optimized pipeline architecture

- Ultra Low Latency

- Ultra-low read latency, even at high utilization

- Exceptionally low write latency provides extra performance gain

- Peak latency suppression through proprietary latency-aware scheduling algorithm

- Active QoS Control

- Dynamic priority control based on observed latency & bandwidth for master IPs

- When combined with ORBIT™ interconnect (OIC) for maximum performance & flexibility.

- Physical-design friendliness

- Support clock domain split between OMC & PHY

- Flexible floorplan of memory controller layout-block

- Highly flexible & configurable DDR controller

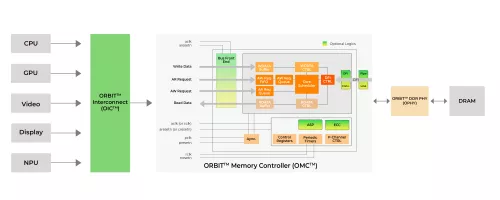

Block Diagram

Applications

- Automotive

- Application Processors

- HPC/Super Computing

- Block Chain/Crypto Currency

- Digital TV

- Data Center

- Game Console

- Entertainment

- Graphic Cards

Deliverables

- OMC is packaged with the following items for all eligible companies:

- IP core RTL

- Standalone Simulation Environment

- Management SW

- IP Documentation

Technical Specifications

Maturity

Silicon Proven & Market Proven

Availability

Now

Related IPs

- I2C Controller IP – Slave, Parameterized FIFO, Hs-Mode (3.4 Mbps) AXI/AHB/APB/Avalon Buses or direct to/from Registers or Memory

- SPI XIP Flash Memory Controller IP – Programmable IO & Execute-In-Place (XIP) via second AMBA Interface

- I2C Controller IP – Master, Parameterized FIFO, APB Bus

- Quad SPI Flash Memory Controller

- I2C Controller IP- Master / Slave, Parameterized FIFO, AXI Bus

- I2C Controller IP- Master / Slave, Parameterized FIFO, AHB Bus