Interconnect IP for TSMC

Welcome to the ultimate Interconnect IP for TSMC hub! Explore our vast directory of Interconnect IP for TSMC

All offers in

Interconnect IP

for TSMC

Filter

Compare

120

Interconnect IP

for TSMC

from 11 vendors

(1

-

10)

Filter:

- 7nm

-

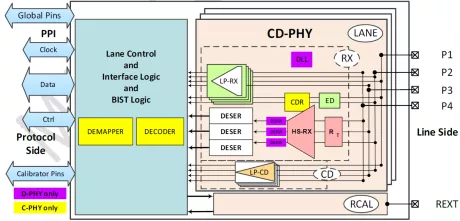

MIPI C-PHY/D-PHY Combo RX IP 4.5Gsps/4.5Gbps in TSMC N7

- Dual mode PHY Supports MIPI Alliance Specification D-PHYv2.5 & C-PHYv2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHYmode

-

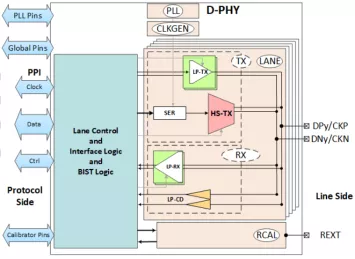

MIPI D-PHY IP 4.5Gbps in TSMC N7

- Supports MIPI Alliance Specification for D-PHY Version 2.5

- Consists of 1 Clock lane and 4 Data lanes

-

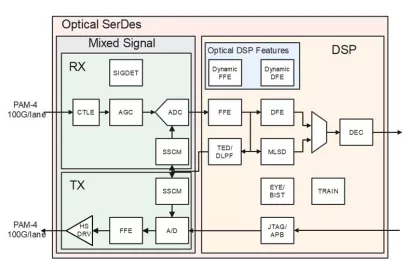

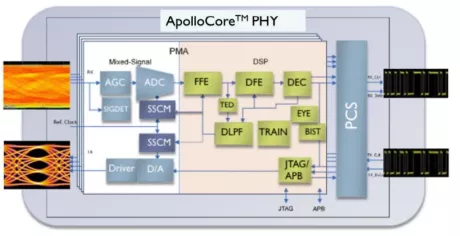

1-112Gbps Integrated Laser Driver and Optical SerDes

- Optical Optimization:

- Integrated laser driver

- RX front-end architected for optical signaling

- Non-linear DSP equalization that corrects for both static and dynamic nonlinearity components.

-

1-112Gbps Medium Reach (MR) and Very Short Reach (VSR) SerDes

- High speed performance

- Low power architecture

- Sub-sampling clock multiplier

-

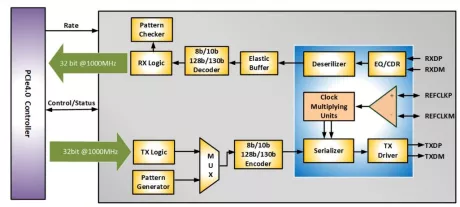

PCIe 5.0 PHY IP for Storage and High-Bandwidth Connection

- Fully compliant with PCI Express Base 5.0 electrical specifications

- Compliant with PIPE5.2 (PCIe) specification

- Supports all power-saving modes (P0, P0s, P1, and P2) defined in PIPE4.4.1 spec

-

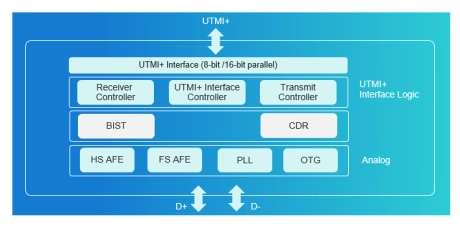

USB 2.0 PHY

- Designed to the USB 2.0 specification, and operates at High Speed (480Mbps), Full Speed (12Mbps), and Low Speed (1.5Mbps)

- Complies with the UTMI v1.05 specification

- Multiple reference clock supported from 9.6MHz up to 52MHz

- 8-bit 60MHz and 16-bit 30MHz parallel interfaces

- Battery Charging Specification v1.2

-

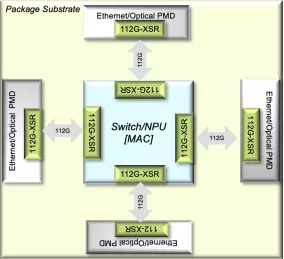

112G-VSR PAM4 SerDes PHY - PPA optimized for short reach connectivity

- 1.25Gbps to 116Gbps flexible data rates allowing simultaneous support of different protocols including Ethernet and OTN

- Power optimized for short-reach applications with configurability

- Superior bit error rate (BER) with extra performance margin beyond short-reach standard requirements

- Beachfront optimized floorplan allows north-south and east-west SoC edge placement

- Comprehensive on-chip diagnostic features make system testing and debugging quick and easy

- Enables 800Gbps networking with PHY and Controller solutions

-

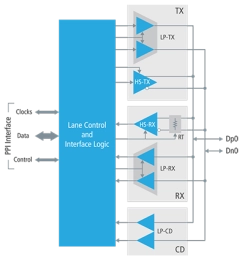

MIPI D-PHY

- Multiple Configurations Possible. TX-only (with integrated PLL), RX-only, and combined TX and RX configurations

- Complete Function for HS TX/RX, LP TX/RX, and LPCD with automatic termination control for high-speed and low-power modes

- Integrated BIST Capable of producing and checking PRBS, CRPAT, and CJTPAT

-

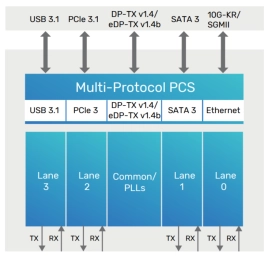

10Gbps Multi-Link and Multi-Protocol PCIe 3.1 PHY IP for TSMC

- Supports USB 3.1, PCIe 3.0/2.0/1.0, DP-TX v1.4/ eDP-TX v1.4b, SATA 3, 10G-KR and SGMII

- Supports PCIe L1 sub-states

- Supports SRIS and internal SSC generation

- Supports internal and external clock sources with clock active detection

-

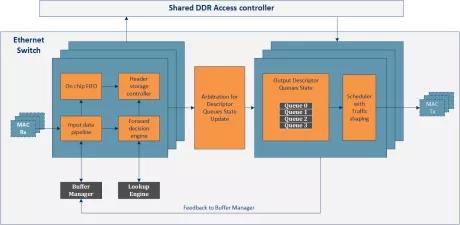

1G Deep Buffering Memory Ethernet Switch IP Core

- Delivers Performance

- Highly Configurable

- Easy to use

- Silicon Agnostic