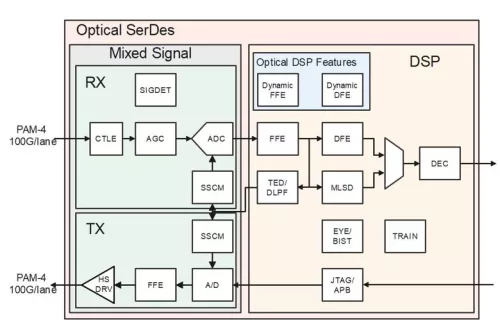

OptiCORE includes all of the features of the AlphaCORE electrical SerDes (low-power high-speed ADC, sub-sampling clock multiplier (SSCM), powerful DSP equalization including FFE and DFE, an optional most likely sequence detector (MLSD), robust equalization training algorithms, a built-in self-test (BIST) mode, and master controller) as well as the features needed for an optical SerDes, including an integrated laser driver, an updated RX front-end optimized for optical signaling, and a non-linear DSP equalization that corrects for both static and dynamic nonlinearity components.

1-112Gbps Integrated Laser Driver and Optical SerDes

Overview

Key Features

- Optical Optimization:

- Integrated laser driver

- RX front-end architected for optical signaling

- Non-linear DSP equalization that corrects for both static and dynamic nonlinearity components.

- Power Optimization:

- Low-power high-speed ADC

- Sub-sampling clock multiplier (SSCM)

- Powerful DSP equalization including FFE and DFE

- Optional most likely sequence detector (MLSD)

- Robust equalization training algorithms

- Built-in self-test (BIST) mode

- Master controller

Benefits

- High-Speed Performance

- OptiCORE builds on the low noise, high speed analog front end IP that delivers performance and configurability to support PAM4 and NRZ signaling, and adds an optimized analog front end for optical signals to improve linearity and noise performance.

- Optical Refinement

- Dynamic equalization techniques were also tailored for optical signals to compensate for dynamic nonlinearity in VCSELs and DMLs due to the different frequency responses at different laser bias currents. These sophisticated techniques improve performance when the received input waveform shows eye skew.

- Sub-sampling clock multiplier

- OptiCORE CDR employs a wide tuning, sub-sampling clock multiplier that can track hundreds of ppm frequency error and provide continuous tracking. Only one common integrated PLL needed for up to 8 channels per side. No off die clean up PLL required, and no clock buffer required to drive off die. This greatly simplifies implementation, saving area and power.

Block Diagram

Technical Specifications

Foundry, Node

N5

Samsung

Pre-Silicon:

5nm

TSMC

Silicon Proven:

5nm

,

6nm

,

7nm

Related IPs

- 622Mbps Laser Driver with Power Control (Vcc=3.3V,Freq=700Mbps, Pulse-Width Distortion=70pS)

- 1-112Gbps Medium Reach (MR) and Very Short Reach (VSR) SerDes

- Integrated Bandgap and Current Reference on TSMC CLN2P

- Integrated Bandgap and Current Reference on TSMC CLN3E

- Integrated Bandgap and Current Reference on TSMC CLN3P-CLN3X

- Integrated Bandgap and Current Reference on TSMC CLN6FF