Interconnect IP

Welcome to the ultimate Interconnect IP hub! Explore our vast directory of Interconnect IP

All offers in

Interconnect IP

Filter

Compare

3,298

Interconnect IP

from 159 vendors

(1

-

10)

-

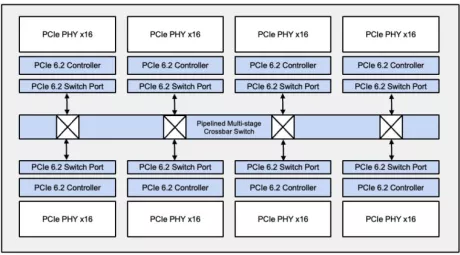

PCIe 6.2 Switch

- 1 upstream port, up to 7 downstream ports

- Up to 128 lanes

- PCIe TLP routing: Configuration, Memory Write/Read, I/O and Messages Packets

- L1 and wake-up events forwarding

-

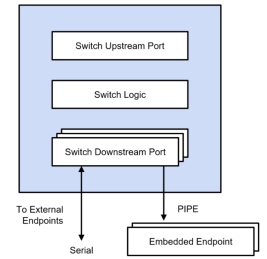

PCIe 7.0 Switch

- Configurable from PCIe 7.0 x8/ PCIe6x16 @1GHz clock down to PCIe 5.0 x1

- Highly scalable with up to 31 configurable external or embedded endpoints

- Configurable Egress Buffer for non-blocking output queueing switch performance

- Flit mode to non-Flit mode conversion

- Low power optimized

- Superior performance through a nonblocking architecture

- Minimized footprint

-

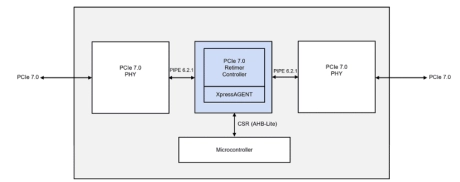

PCIe 7.0 Retimer Controller with CXL Support

- Supports PCIe 7.0 128 GT/s speeds at up to x16 lanes

- CXL 3.0 aware

- Supports PIPE 6.2.1 compatible PHYs

- Optimized for low latency

- Highly-configurable equalization algorithms and adaptive behaviors

-

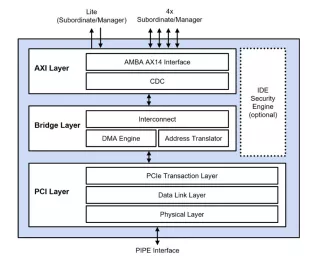

PCIe 7.0 Controller with AXI

- Optimized for high-bandwidth efficiency at data rates up to 128 GT/s

- Separate native TX/RX data path separating posted/Non posted/completion traffic

- Handles up to 4 TLPs per cycle

- Advanced PIPE modes and port bifurcation

-

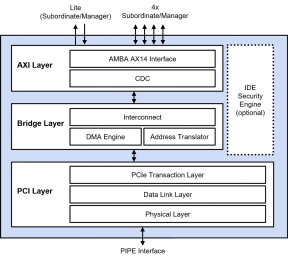

PCIe 7.0 Controller

- Optimized for high-bandwidth efficiency at data rates up to 128 GT/s

- Separate native TX/RX data path separating posted/Non posted/completion traffic

- Handles up to 4 TLPs per cycle

- Advanced PIPE modes and port bifurcation

-

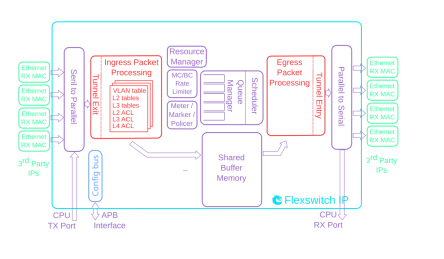

Ethernet Enterprise Switch/Router IP Core - Efficient and Massively Customizable

- Full wire-speed on all ports and all Ethernet frame sizes.

- Store and forward shared memory architecture.

- Support for jumbo packets up to 32739 bytes.

-

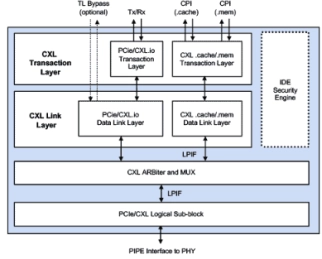

CXL 3.1 Controller

- Ultra-low Transmit and Receive latency

- Internal data path size automatically scales up or down (256, 512 or 1024 bits) based on max. link speed and width for optimal throughput

- Supports backwards compatibility to PCIe 6.1

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Optional QuickBoot mode allows for up to 4x faster link training, cutting system-level simulation time by 20%

- Loopback Mode support at DLL for CXL.mem and CXL.cache protocols

- Merged Replay and Transmit buffer enables lower memory footprint

-

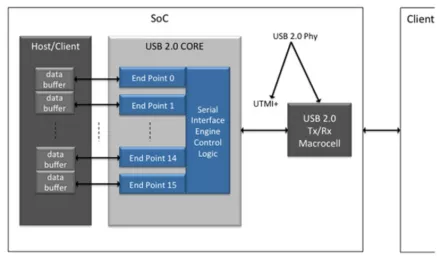

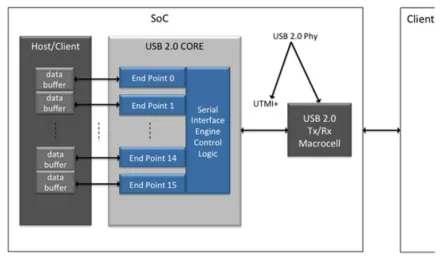

USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- Complies with USB specifications Rev. 2.0 and 1.1

- Complies with UTMI+ specification Level 3, Rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- Complies with USB specifications Rev. 2.0 and 1.1

- Complies with UTMI+ specification Level 3, Rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

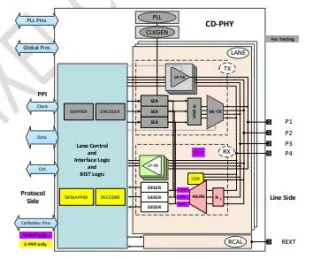

MIPI C-PHY/D-PHY Combo CSI-2 RX+ IP (6.0Gsps/trio, 4.5Gbps/lane) in TSMC N6

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode