JESD204 IP

Welcome to the ultimate JESD204 IP hub! Explore our vast directory of JESD204 IP

All offers in

JESD204 IP

Filter

Compare

38

JESD204 IP

from 11 vendors

(1

-

10)

-

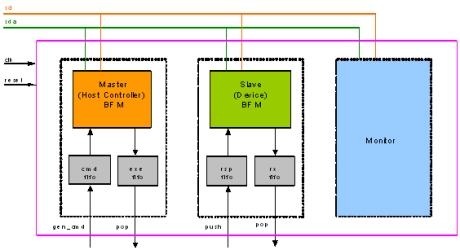

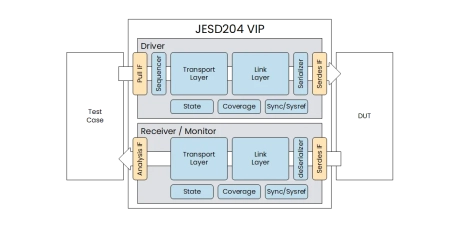

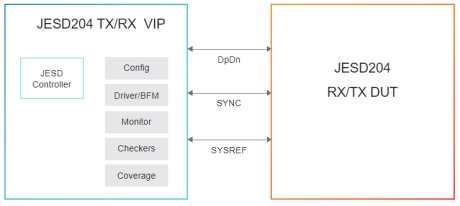

JESD204 Verification IP

- This JESD204 Verification IP provides an advanced and efficient solution for verifying and debugging these standards in a UVM simulation environment.

- The verification IP helps reduce time to test, accelerate verification process and ensures a high quality for the end-product.

-

JESD204D Controller IP

- Line rates up to 116 Gbps

- Supports 1-24 lanes

- Supports 1-96 converters

- HD-mode supported

-

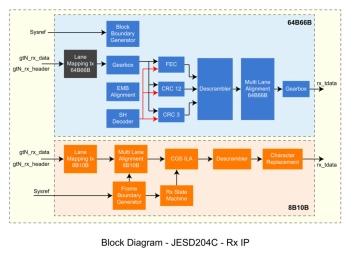

JESD204C Controller IP

- Designed to JEDEC JESD204C.1 specification

- Line rates from 1 Gbps to 32.5 Gbps

- Supports 1-24 lanes

- Supports 1-96 converters

-

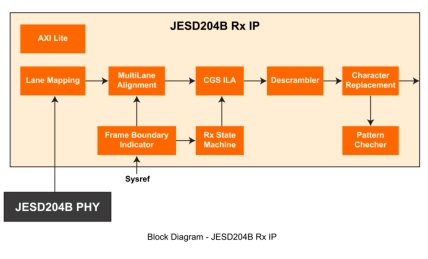

JESD204B Controller IP

- Designed to JEDEC JESD204B.01 specification

- Line rates from 1 Gbps to 12.5 Gbps (with optional extension to 16 Gbps)

- Supports 1-24 lanes

- Supports 1-96 converters

-

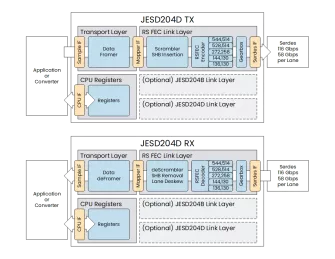

JESD204D Transmitter and Receiver IP

- Designed according to JEDEC JESD204D Standard.

- Supports up to 24 lanes per IP cores.

- Supports new link layer using Reed-Solomon Forward Error Correction (RS-FEC).

- Option for backward compatibility to JESD204C (supports 64B/66B encoding) and JESD204B (supports 8B/10B encoding).

-

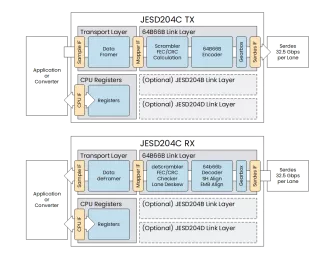

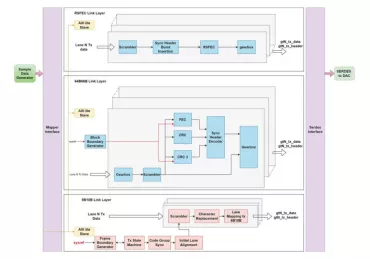

JESD204C Transmitter and Receiver

- With the addition of error correction and Detection(FEC, CRC), cutting-edge instrumentation and other applications can operate without any errors.

- Offers better DC balance, clock recovery and data alignment compared to JESD204B.

- The bit overhead is 3.125% which is much smaller than JESD204B (~ 25%).

- Provides interface for serializing devices from some system designs, reducing space, power, and cost.

-

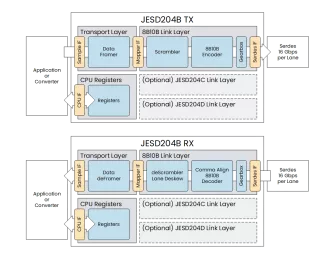

JESD204B Transmitter and Receiver

- Applicable in RADAR, Medical Imaging as it supports higher bandwidth and more number of channels with fewer pins to simplify layout.

- Applicable in Wireless Communications, TDMA & OFDM based technologies such as LTE, WiMAX can benefit from high frequency scalability provided by JESD204B.

- JESD204B is necessary for high density systems as it provides reduced PCB area and package size.

- Comparable power for large throughput.

-

Simulation VIP for JESD204

- Topology

- Transmitter or receiver configuration

- Clock Frequency

- Any frequency is supported, as the VIP works on the source clock

-

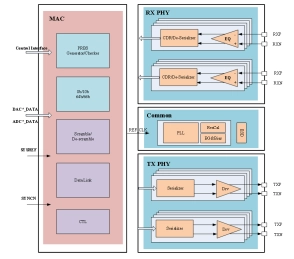

JESD204B/204C IP with PHY and MAC layer

- X4/X8 Lane Mode, support up to 25Gbps (per lane)

- Shared common PLL based architecture

- Digitally-control-impedance termination resistors and On-chip resistance calibration

- Configurable TX output differential voltage swing

-

JESD403 VIP

- Compliant with JESD403 version 1.0 specification.

- Full JESD403 Host Controller and Device functionality.

- Two wire serial interface up to 12.5 MHz.

- Supports Dynamic Address Assignment including Static Addressing for legacy I2C Devices.