CPRI IP Cores

Welcome to the ultimate CPRI IP hub! Explore our vast directory of CPRI IP cores

The Common Public Radio Interface (CPRI) IP cores implement the CPRI Specification. CPRI is a high-speed serial interface for network radio equipment controllers (REC) to receive data from and provide data to remote radio equipment (RE).

All offers in

CPRI IP Cores

Filter

Compare

19

CPRI IP Cores

from 7 vendors

(1

-

10)

-

eCPRI

- Delivers Performance

- Highly Configurable

- Silicon Agnostic

- Easy to use

-

CPRI Master and Slave

- Provides a framework to facilitate Radio Equipment products development for mobile telecommunications systems.ant to Display Port 2.0/eDP1.5.

- It supports multiple data rates up to 24.33024 Gbps.

- All the Base station manufacturers can use one standard protocol.

- Targets high-performance, remote radio network applications.

-

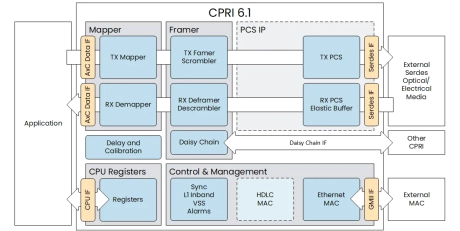

CPRI 6.1

- Delivers Performance

- Highly Configurable

- Easy to use

- Silicon Agnostic

-

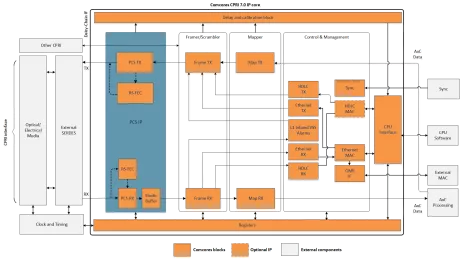

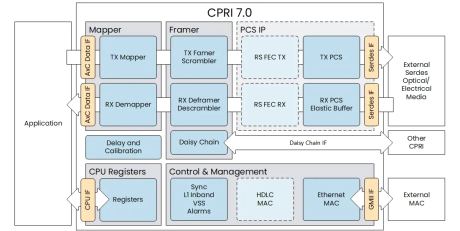

CPRI 7.0

- CPRI Specification V7.0 full feature set

- All mapping methods available (2 is optional)

- Accurate delay measurements and calibration

-

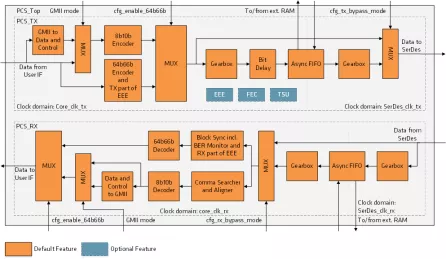

Ethernet 1G/2.5G/5G/10G/25G and CPRI 7.0 PCS

- Delivers Performance

- Feature Rich

- Highly Configurable

- Silicon Agnostic

-

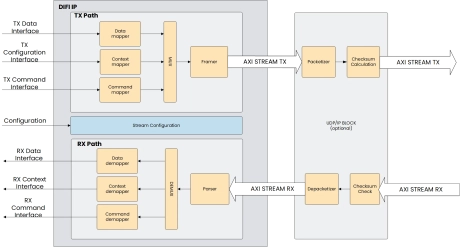

DiFi IP core

- The DiFi IP core is a highly scalable and silicon agnostic implementation of the IEEE-ISTO Std 4900-2021: Digital IF Interoperability Standard v1.2.1 targeting ASIC, and FPGA technologies.

- The DiFi implementation builds on long-time experience designing IP cores for sending and receiving Radio IQ data over Ethernet networks, and delivers a flexible engine that is prepared for tight integration with software applications.

-

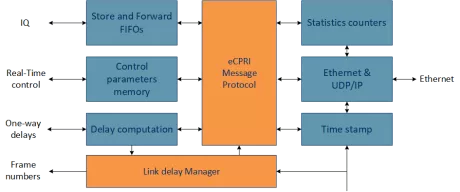

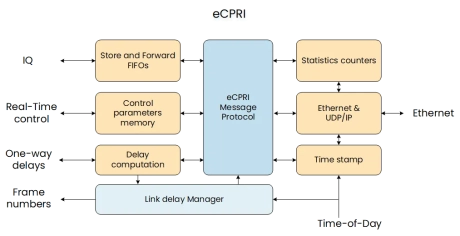

eCPRI

- eCPRI core is a highly scalable and silicon agnostic implementation of the eCPRI standard targeting any ASIC or FPGA technologies.

- The eCPRI implementation builds on Chip Interfaces long-time experience designing CPRI and Radio-Over-Ethernet solutions for fronthaul and delivers a flexible engine that is prepared for tight integration with software applications.

-

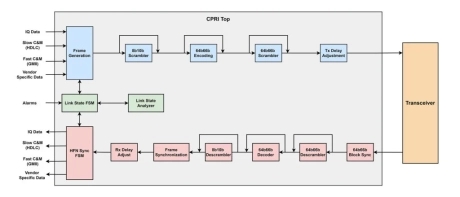

CPRI 7.0

- The Common Public Radio Interface (CPRI) 7.0 core is a silicon agnostic implementation of the CPRI 7.0 specification, which is targeting both ASIC and FPGAs CPRI.

- CPRI is a high-speed serial interface designed to meet or exceed the requirements of base band systems, C-RAN switches, Digital Front-End (DFE) processors or advanced test systems.

- With its extreme flexibility and reduced logic consumption, the CPRI 7.0 IP core is the perfect match whether the application is REC (Radio Equipment Controller) or RE (Radio Equipment).

-

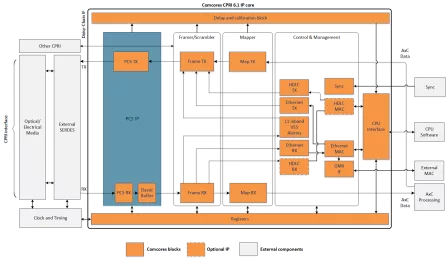

CPRI 6.1

- Common Public Radio Interface (CPRI) 6.1 core is a silicon agnostic implementation of the CPRI 6.1 specification, which is targeting both ASIC and FPGAs.

- CPRI is a high-speed serial interface designed to meet or exceed the requirements of base band systems, C-RAN switches, Digital Front-End (DFE) processors or advanced test systems.

-

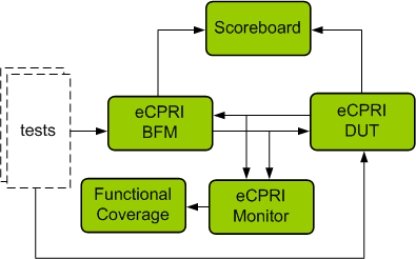

eCPRI Verification IP

- Compliant with eCPRI Specification V2.0.

- Complete eCPRI Tx/Rx functionality.

- Supports the eCPRI layer of the eCPRI specification.

- Supports 5G and enables increased efficiency.