MIL-STD-1553 IP

Welcome to the ultimate MIL-STD-1553 IP hub! Explore our vast directory of MIL-STD-1553 IP Cores.

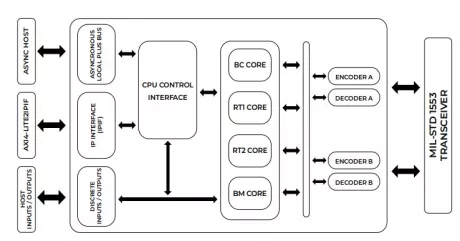

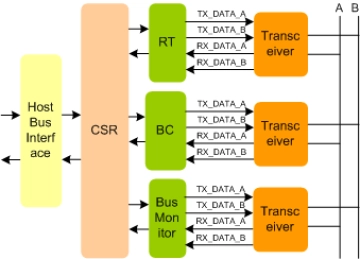

MIL-STD-1553B IP Cores implements MIL-STD1553B standard and provide single or multifunctional interface between host processor and MIL-STD-1553 bus transceiver.

DO-254 compliant MIL-STD-1553B IP cores can function as Bus Controller (BC), two separate Remote Terminals (RT) and Bus Monitor (BM), simultaneously.

All offers in

MIL-STD-1553 IP

Filter

Compare

11

MIL-STD-1553 IP

from 8 vendors

(1

-

10)

-

DO-254 compliant MIL-STD-1553B IP core

- 64K bytes internal static RAM with RAM Error Detection/Correction option

- 16-bit time tag counters and clock sources for all terminals

-

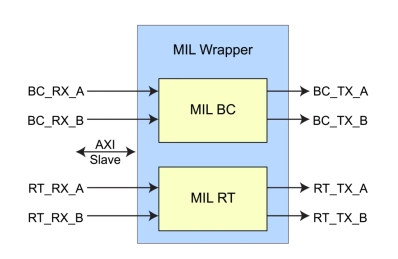

MIL1553B IP Core

- High bit error reliability

- Dual redundancy : Two buses supported

- BC, RT and BM Modes are supported.

-

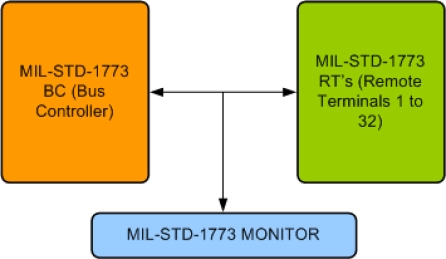

MIL STD 1773 Verification IP

- Compliant with MIL STD 1773 Standard.

- Supports Bus Controller (i.e,BC), Remote Terminal (i.e,RT) and Bus Monitor (i.e,BM) operation.

- Supports Single/Dual/Quad channel, dual redundant bus communication modules.

- Supports configurable length of word length, default 20 bits.

-

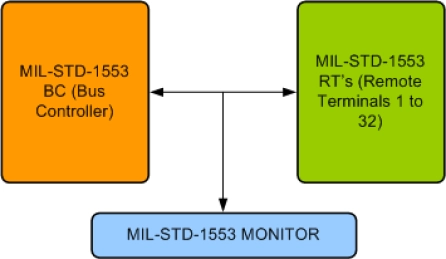

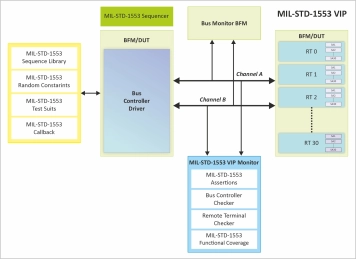

MIL STD 1553 Verification IP

- Compliant with MIL STD 1553B Standard.

- Supports Bus Controller (i.e,BC), Remote Terminal (i.e,RT) and Bus Monitor (i.e,BM) operation.

- Supports Single/Dual/Quad channel, dual redundant bus communication modules.

- Supports configurable length of word length, default 20 bits.

-

MIL STD 1553 Controller IIP

- Compliant with MIL STD 1553B specification

- Supports Remote terminal, Bus Controller and Bus monitor

- Supports configurable length of word length, default 20 bits

- Supports configurable length of data bits, default 16 bits

-

MIL-STD-1553 Verification IP

- Supports up to 31 Remote Terminals (devices).

- Supports up to 30 sub-addresses (sub-system).

- Supports multiple (commonly dual) redundant buses.

- Supports Dual Pins for multiple (commonly dual) redundant buses.

-

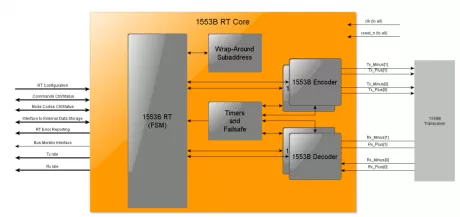

DO-254 MIL-STD-1553B Remote Terminal

- Design Assurance Level A according to RTCA DO-254/ED-80 (April, 2000)

- Fully Compliant to the MIL-STD-1553B, 21 September 1978 (with Notices 1 through 7)

- Configurable number of Buses

- Tested as specified in the MIL-HDBK-1553A, 1 November 1988 (AS4111 Rev. D)

-

MIL-STD-1553 Bus Controller, Remote Terminal, and Monitor Terminal

- Mil-Std-1553 Intellectual Property for FPGAs and ASIC

- Suitable for any Mil-Std-1553 BC, RT, MT implementation

-

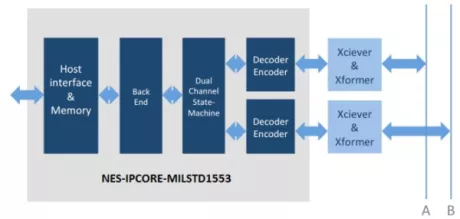

Mil-Std-1553B/AS15531 Interface

- General

- Bus Controller

- Remote Terminal

- Bus Monitor

-

AMBA interface for Actel MIL-STD-1553B Cores

- AMBA AHB interface for Actel B1553BC/RT/BRM cores

- AMBA AHB master interface

- No block RAM needed

- Low CPU overhead due to DMA transfers