Video Interface IP

Welcome to the ultimate Video Interface IP hub! Explore our vast directory of Video Interface IP

All offers in

Video Interface IP

Filter

Compare

147

Video Interface IP

from 29 vendors

(1

-

10)

-

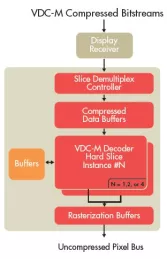

VESA VDC-M Decoder

- VESA Display Compression-M (VDC-M) 1.2 compliant

- Supports all VDC-M encoding mechanisms: BP, transform, MPP, MPP fallback, BP skip, flatness detection and signaling

- Configurable maximum display resolution of up to 16Kx16K

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, or 12 bits per component video

- 4:4:4 sampling for RGB video input format

-

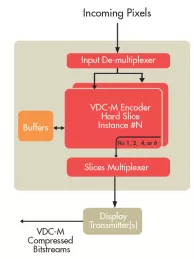

VESA VDC-M Encoder

- VESA Display Compression-M (VDC-M) 1.2 compliant

- Supports all VDC-M encoding mechanisms: BP, transform, MPP, MPP fallback, BP skip, flatness detection and signaling

- Configurable maximum display resolution of up to 16Kx16K

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, or 12 bits per component video

-

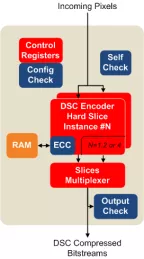

VESA DSC 1.1 Encoder IP Core for Automotive Displays (ASIL-B Ready ISO 26262 Certified)

- VESA DSC 1.1 compliant

- Supports all DSC 1.1 mandatory encoding mechanisms

- Configurable maximum display resolution

-

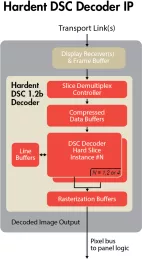

VESA DSC Decoder

- VESA Display Stream Compression (DSC) 1.2b compliant

- Supports all DSC 1.2b mandatory encoding mechanisms: MMAP, BP, MPP, and ICH

- Output buffering compatible with transport stream over video interfaces

- Configurable maximum display resolution

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, 12, 14, and 16 bits per video component

-

VESA DSC Encoder

- VESA Display Stream Compression (DSC) 1.2b compliant

- Supports all DSC 1.2b mandatory encoding mechanisms: MMAP, BP, MPP, and ICH

- Output buffering compatible with transport stream over video interfaces

- Configurable maximum display resolution

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, 12, 14, and 16 bits per video component

- YCbCr and RGB video input format

- 4:4:4, 4:2:2, and 4:2:0 native coding

-

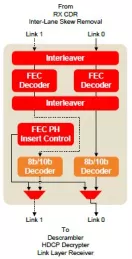

DisplayPort 1.4 FEC Receiver (Rx)

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

- Status and control can be done with signals or optionally via an integrated APB register module (Rx)

-

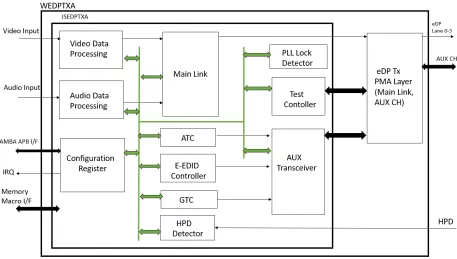

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 12FFC

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channel

-

eDP1.4/DP1.3 TX Link IP

- eDP version 1.4a, DP version 1.3 compliant receiver

- Supports HDCP Decryption

- Supports both 1.62/8.1Gbps data rate

-

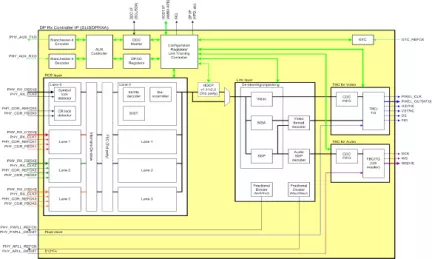

VESA Display Stream Compression (DSC) IP Core

- Supports Versions 1.1, 1.2 and 1.2a

- Supports RGB and YCbCr color spaces

- 1-to-8 slice support

-

Intra-Panel Low-Power TX 28nm

- COG and COF transmitter

- Data Rate : 120M ~ 3.2Gbps

- Power Down Mode