Error Correction/Detection IP

Error Correction/Detection IP cores are specialized hardware modules designed to enhance the reliability and integrity of data transmission and storage in embedded systems. These cores implement advanced error detection and correction algorithms, such as Hamming codes, Reed-Solomon, and BCH, to identify and correct errors in data, ensuring accurate and secure communication. Ideal for applications in memory systems, communication networks, and high-performance computing, Error Correction/Detection IP cores help prevent data corruption, reduce system downtime, and improve overall system performance.

All offers in

Error Correction/Detection IP

Filter

Compare

249

Error Correction/Detection IP

from 40 vendors

(1

-

10)

-

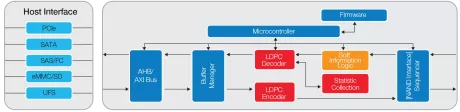

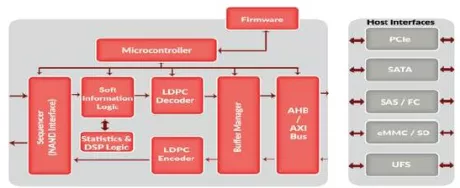

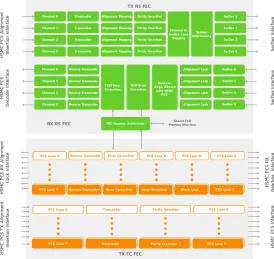

eMMC LDPC Encoder/Decoder

- Supports data rates from 50 MB/s to 9.0 GB/s.

- Enables custom LDPC core development for specific requirements.

- Wide range of codeword sizes.

- Maximum supported parity.

-

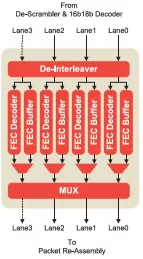

HDMI 2.1 FEC Receiver (Tx)

- HDMI 2.1 compliant

- Reed-Solomon RS (255,251) FEC, 8-bit symbols

- Supports 3-lane and 4-lane operation

- Error counters included (Rx only)

-

LDPC Encoder/Decoder (LDPC)

- Supporting a wide range of data-rates

- 50MB/s to 4.0GB/s for a single LDPC instance

- Scalable platform provides the basis for customer specific custom-LDPC cores

-

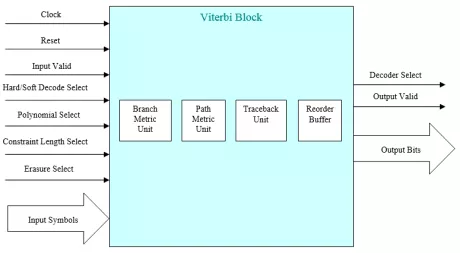

Viterbi Decoder

- Hard or soft decoder with configurable soft bit widths

- Parameterisable generator polynomials

- Parameterisable code Constraint length

-

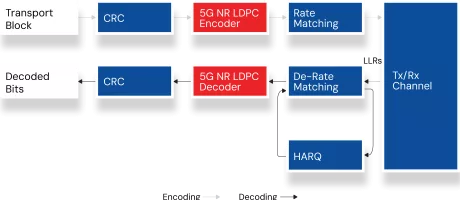

LDPC Decoder for 5G NR and Wireless

- Feature rich, highly flexible, scalable, configurable and timing friendly design

- Ease of integration

- Compliance with 3GPP Standards

-

-

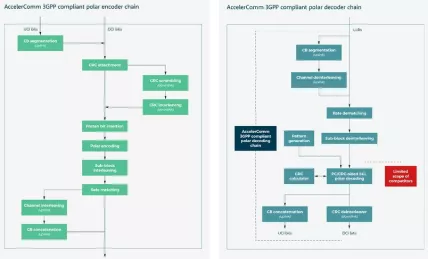

Polar Encoder / Decoder for 3GPP 5G NR

- Fully compliant with the 3GPP NR standard for PUCCH, PUSCH, PDCCH and PBCH. Supports the full range of uncoded and encoded block sizes

- Implements the entire Polar encoding and decoding chain in 3GPP TS38.212

- High error correction performance from Polar PC/CRC-aided decoder core

- Tightly integrates the components in the chain to reduce area usage and latency

-

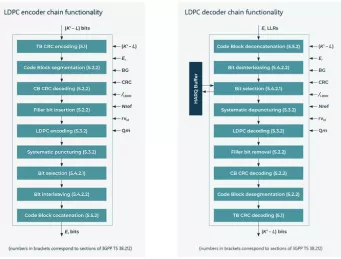

LDPC Encoder / Decoder for 3GPP 5G NR

- Fully compliant with the 3GPP NR standard for PDSCH, PUSCH. Supports the full range of uncoded and encoded block sizes

-

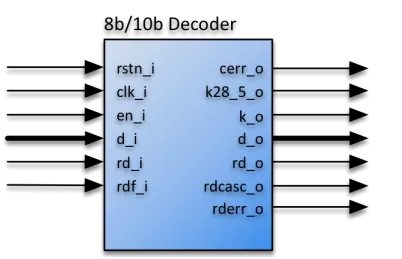

8b/10 Decoder

- 8b10b decoding

- Can be cascaded for 16b20b decoding

- Supports industry standard comma “K” symbols

- Pipelined design

-

Reed Solomon Encoder

- Parameterizable bits per symbol

- Programmable codeword length

- Programmable number of errors