USB IP

Welcome to the ultimate USB IP hub! Explore our vast directory of USB IP

All offers in

USB IP

Filter

Compare

751

USB IP

from 50 vendors

(1

-

10)

-

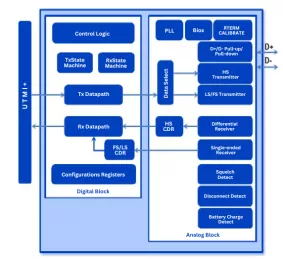

USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- Complies with USB specifications Rev. 2.0 and 1.1

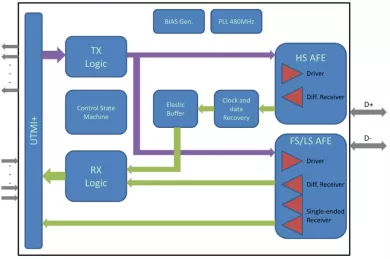

- Complies with UTMI+ specification Level 3, Rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- Complies with USB specifications Rev. 2.0 and 1.1

- Complies with UTMI+ specification Level 3, Rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

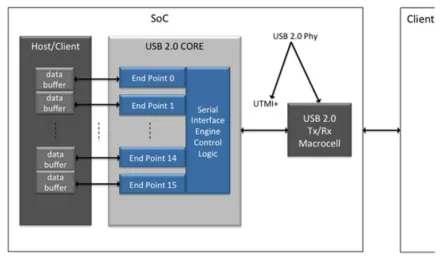

Complete USB Type-C Power Delivery IP

- Mixed signal Analog Front End Macros for 65n, 130n, 150nm, and 180n technologies.

- RTL code from AFE to I2C compatible register set.

- Stand alone C code for Protocol, Device Policy Manager, and System Policy Manager.

- IP demonstration & development board, with compliance reports.

- Full chip integration of USB Type-C, and associated software.

-

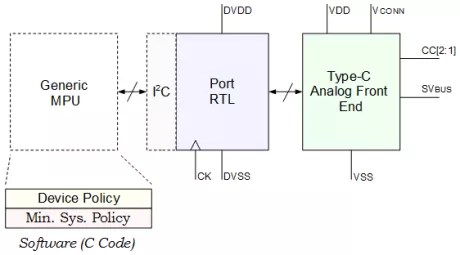

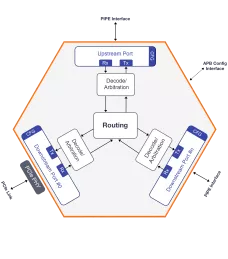

PCIe Switch for USB4

- Fully transparent design eliminates the need for Host configuration and management software

- Built-in support for PIPE-attached embedded endpoints (including 64-bit PIPE) for reduced BoM, latency, and power

- Seamless implementation on ASIC and FPGA with same RTL code base, up to x8 Gen4 per port on FPGA (or x16 Gen3)

- Lowest latency switching logic on the market (2 clock cycles)

-

USB 2.0 PHY IP, Silicon Proven in TSMC 22ULP

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

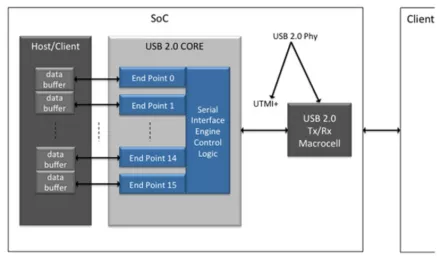

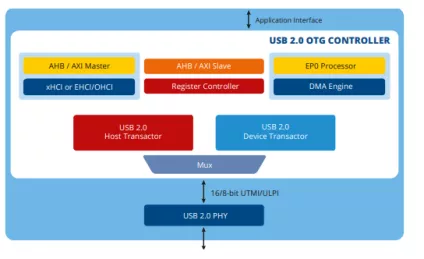

USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- Support SW controlled host/device role switching.

- Support Fullspeed and Lowspeed

- Support Control, Bulk, Interrupt and Isochronous Transfer Types

- Support L1/L2 power saving modes for USB 2.0 port

-

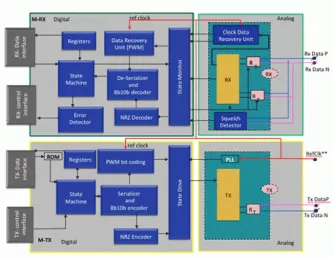

MIPI M-PHY - TSMC 40nm

- Compliant to MIPI Alliance Standard for M-PHY specification Version 3.0

- •Supports high speed data transfer G1A/B, G2A/B and G3A/B with data rates of up to 5830.4 Mbps

- •Supports M-PHY Type-I system

- •Support for reference clock frequencies of 19.2MHz/26MHz/38.4MHz/52MHz

-

USB 2.0 PHY

- Complies with USB specifications, rev. 2.0 and 1.1

- Complies with UTMI+ specification, level 3, rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

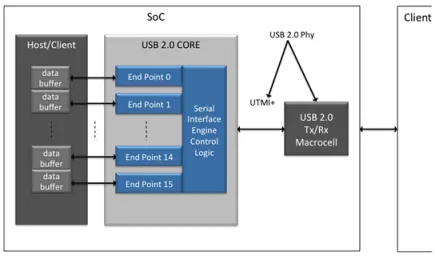

USB2.0 PHY, 8-bit or a 16-bit parallel interface, remaining backward compatible with USB1.1 legacy protocol at 12Mbps

- Complies with Universal Serial Bus Specification Rev. 2.0

- Interface compliant with the UTMI specification (60MHz 8-bit interface or 30MHz 16-bit interface)

- Supports 480Mbps High-Speed(HS) and 12Mbps Full-Speed(FS)

-

SD4.1 UHS- II PHY IP

- SD 4.1 compliant SDHC/SDXC UHS-II Physical Layer for Host

- 16bit interface to Link layer

- Supports both Full Duplex mode and Half Duplex mode