Forward Error Correction IP

Welcome to the ultimate Forward Error Correction IP hub! Explore our vast directory of Forward Error Correction IP

All offers in

Forward Error Correction IP

Filter

Compare

88

Forward Error Correction IP

from 19 vendors

(1

-

10)

-

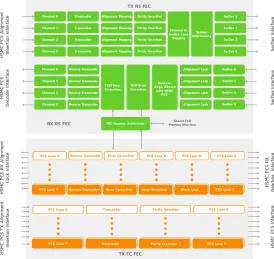

HDMI 2.1 FEC Receiver (Tx)

- HDMI 2.1 compliant

- Reed-Solomon RS (255,251) FEC, 8-bit symbols

- Supports 3-lane and 4-lane operation

- Error counters included (Rx only)

-

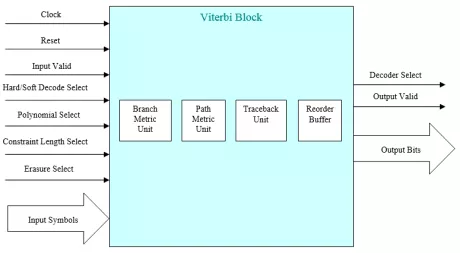

Viterbi Decoder

- Hard or soft decoder with configurable soft bit widths

- Parameterisable generator polynomials

- Parameterisable code Constraint length

-

-

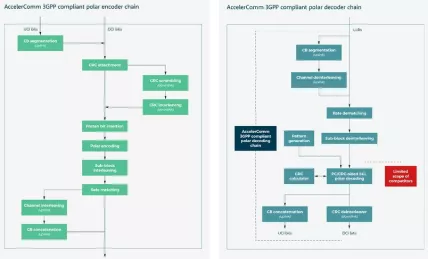

Polar Encoder / Decoder for 3GPP 5G NR

- Fully compliant with the 3GPP NR standard for PUCCH, PUSCH, PDCCH and PBCH. Supports the full range of uncoded and encoded block sizes

- Implements the entire Polar encoding and decoding chain in 3GPP TS38.212

- High error correction performance from Polar PC/CRC-aided decoder core

- Tightly integrates the components in the chain to reduce area usage and latency

-

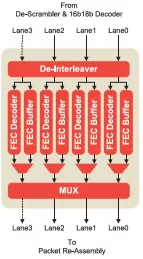

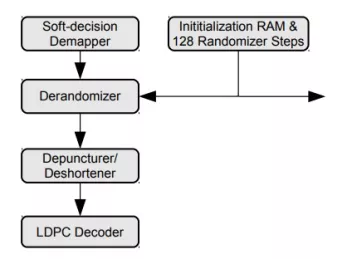

DOCSIS 3.1 LDPC Decoder (PLC / NCP / Data)

- Soft-Decision Demapper, Derandomizer, Deinterleaver, Depuncturer, and LDPC Decoder are included

- Support for 4k and 8K FFT sizes

- Support for 16-QAM modulation

-

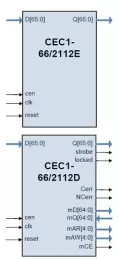

66/2112 Codec for Cyclic Code (2112,2080)

- Small Size

- Implements FEC Sublayer for 10GBASE-R (section 74 of the IEEE 802.3 standard)

- 10G/40G/100G Ethernet MAC-friendly interface

- Practically self-contained: requires only memory for one 2112-bit block in the decoder.

-

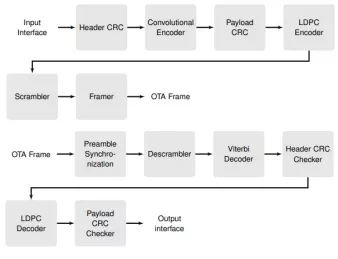

SDA OCT V3.0 Encoder and Decoder

- Compliant with "Optical Communications Terminal (OCT) Standard Version 3.0, Document ID: SDA-9100-0001-05, August 2021"

- Support for payload code rates 11/13, 22/29, 2/3, 1/2, and uncoded data

-

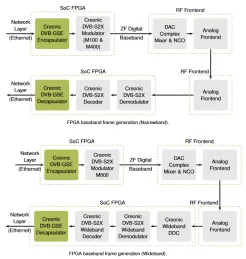

DVB-GSE Encapsulator and Decapsulator

- Compliant with ETSI TS 102 606-1 V1.2.1 (Annex D, DVB-GSE Lite)

- Support for multi-protocol encapsulation (IPv4, IPv6, MPEG, Ethernet, etc.)

-

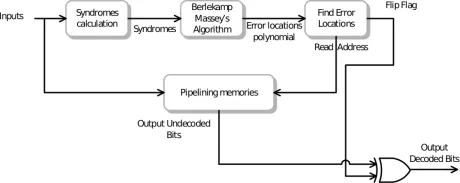

BCH Encoder/Decoder

- BCH decoder compliant with the DVB-T2/S2 standard.

- Available for Altera/Xilinx FPGA or ASIC implementation.

- High speed design.

- BCH decoder works on GF(2M) where M = 16 or 14 and correctup to T errors where T = 10 or 12.

-

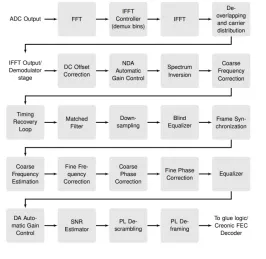

DVB-S2X Multi-Carrier Demodulator

- Supports CCM, ACM and VCM

- Supports roll-off factors 5%, 10%, 15%, 20%, 25% to 35%

- Support for short and normal blocks (16,200 bits and 64,800 bits) with pilots only

- Support for QPSK to 256-APSK