Viterbi IP

Welcome to the ultimate Viterbi IP hub! Explore our vast directory of Viterbi IP

All offers in

Viterbi IP

Filter

Compare

25

Viterbi IP

from 15 vendors

(1

-

10)

-

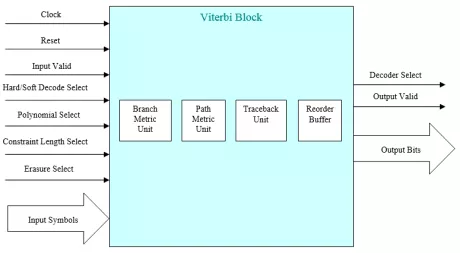

Viterbi Decoder

- Hard or soft decoder with configurable soft bit widths

- Parameterisable generator polynomials

- Parameterisable code Constraint length

-

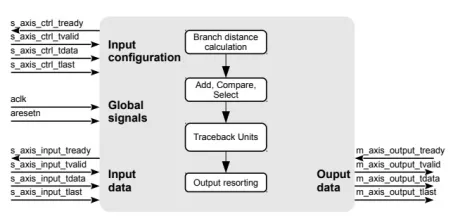

Configurable Viterbi Decoder

- Support for zero-tail and tail-biting Viterbi decoding algorithms.

- Configurable constraint length.

- Configurable trace-back depth.

- Configurable code rate and soft bits.

-

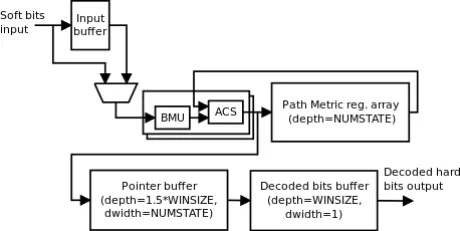

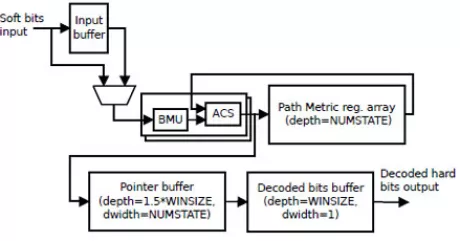

Generic Open Source Viterbi Decoder

- Design-time configuration of encoder polynomials (different number of states and different code rates).

- Support for recursive and non-recursive convolutional codes.

- Windowing technique for reduced latency and memory requirements (with acquisition).

- Design-time configuration of quantization, maximum window size, RAM usage (distributed RAM vs. Block RAM).

-

Viterbi Decoder

- Supports 1/N coderates

- Configurable constraint length

- Configurable generator polynomials

- Configurable precision of state metrics

-

Viterbi Decoder

- Supports 1/N coderates

- Configurable constraint length

- Configurable generator polynomials

- Configurable precision of state metrics

-

Viterbi Decoder

- Parameterizable Viterbi decoder

- Available for ispXPGA and ORCA 4

- Single clock synchronous design

- Soft decision with parameterizable soft width

-

WCDMA Release 9 compliant Viterbi Decoder

- 3GPP TS 25.212 V 9.5.0 Release 9

- Supports all block sizes i.e., K=40 - 504.

- Constraint length of 9

-

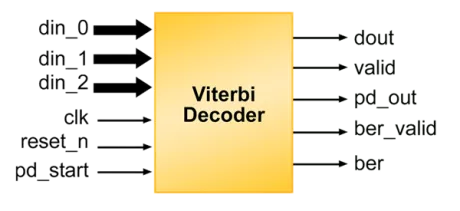

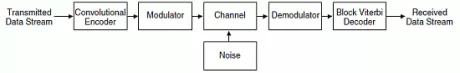

Block Viterbi Decoder

- Compatible with IEEE 802.16-2004 SC PHY/ OFDM PHY, IEEEE802.11a, 3GPP, 3GPP2, and DVB standards

- Supports multiple code rates: 1/2, 1/3, ... 1/7 for non-punctured codes, 2/3, 3/4, ..., 12/13 for punctured codes, and from m/(m+1) to m/(2m-1), where m is from 1 to 12, for dynamic punctured codes

- Variable constraint length from 3 to 9

- Supports dynamically variable code rates and puncture patterns

-

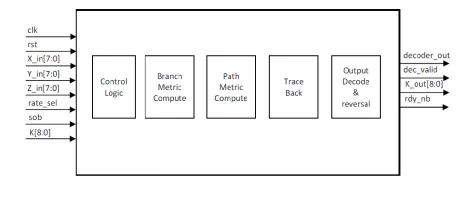

Viterbi decoder for 3GPP WCDMA and 3GPP-LTE

- LTE Rate matching support

- parameterized traceback length

- on-the-fly change of mode, block length, code rate and traceback length

- no external memory required

-

LTE / WiFi Viterbi decoder

- Scalable throughput/area level, selectable prior Core synthesis (3 levels)

- High throughput reachable(1-2 Gbps)