SAS IP

Welcome to the ultimate SAS IP hub! Explore our vast directory of SAS IP

All offers in

SAS IP

Filter

Compare

11

SAS IP

from 5 vendors

(1

-

10)

-

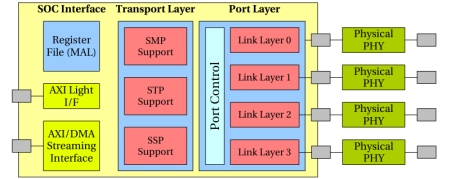

SAS Initiator, 12G, 4 Ports, 48 Gbps

- The SAS Initiator Controller IP Core provides an interface to high-speed serial link replacement for the parallel SCSI attachment of mass storage devices.

- Maximum supported bandwidth is 48 Gbps. The serial link employs multiple high-speed gigabit transceivers.

-

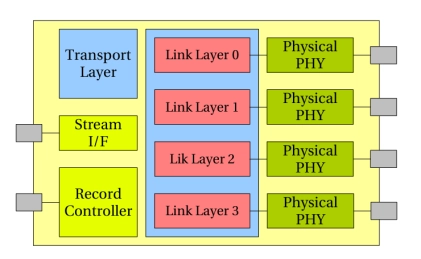

SAS 4 Port 12G Recorder

- High Speed Data Recording

- Up to 4 Ports

- SAS 1.5, 3.0, 6.0 and 12.0 Gbps support

- High Data Bandwidth

- Hardware managed command sequencing

-

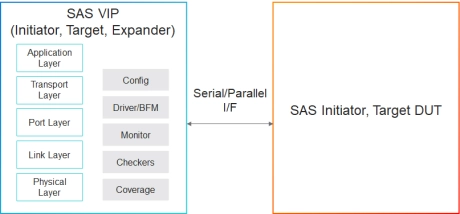

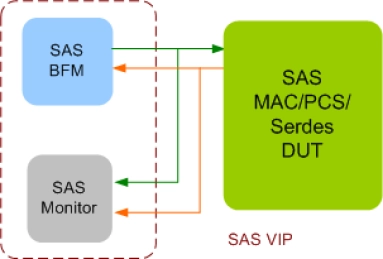

Simulation VIP for SAS

- Device type

- Initiator, Target, and Expander

- Operating Modes

- Supports all SAS speeds: 1.5, 3, 6, 12, 24Gb/s

-

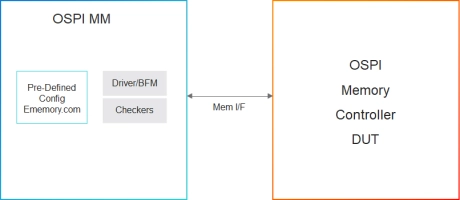

Simulation VIP for OSPI NOR

- Device Density

- From 256Mb to 2Gb, with frequency up to 133MHz in SPI and 200MHz in OSPI mode

- Operation Mode

- Extended SPI mode, Octal SDR and DDR mode (Single I/O and Octal I/O)

-

SAS Verification IP

- Supports trained 1.5,3,6,12 and 22.5 Gbps speeds.

- Supports untrained 1.5,3 and 6 Gbps speeds.

- Supports Narrow ports and wide ports.

- Supports Reset sequences

-

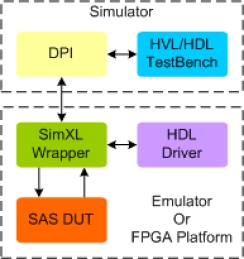

SAS Synthesizable Transactor

- Supports trained 1.5,3,6,12 and 22.5 Gbps speeds.

- Supports untrained 1.5,3 and 6 Gbps speeds.

- Supports Narrow ports and wide ports.

- Supports Reset sequences

-

SAS INITIATOR IIP

- Supports SPL 1.0/2.0/3.0/4.0/5.0 Specs

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

-

Bi-directional High speed interface lane up to 12.5Gbps

- High data rate (Up to 12.5Gbps per lane)

- Programmable receiver frontend

- Programmable transmitter

- 5-bit controlled digital delay line in the receiver for high-speed clock

-

SAS 1-to-1 Speed Bridge with Sandbox

- • Allows users to intercept data between the SAS Host and Device

- • Fully compliant to SAS Gen-3 (12GHz) industry specifications.

- • With correct FPGA, Bridge is capable of SAS Gen-3 (12GHz)

- • Industry proven and compliant SAS interfaces

-

SAS Target Core

- Fully compliant to the SAS 3.0Gb/s, 6.0 and 12.0Gb/s industry specifications

- Processor specific interfaces for register access

- Supports either SerDes, PIPE, or SAPIS interface

- Synchronous design for easy integration