LPDDR4 IP

Welcome to the ultimate LPDDR4 IP hub! Explore our vast directory of LPDDR4 IP

All offers in

LPDDR4 IP

Filter

Compare

79

LPDDR4 IP

from 12 vendors

(1

-

10)

-

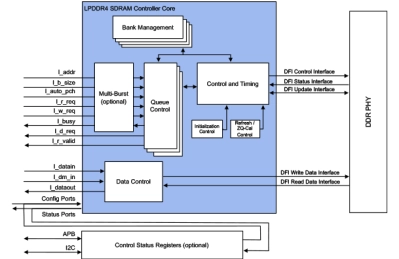

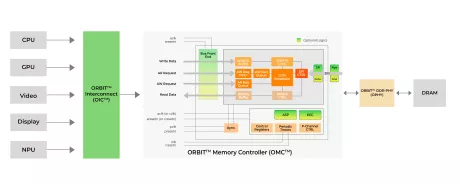

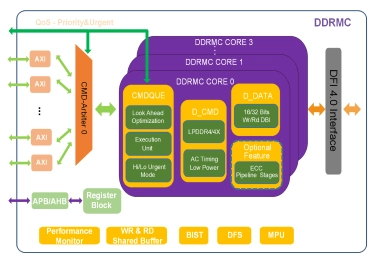

LPDDR4X / LPDDR4 Controller

- Maximizes bus efficiency via look-ahead command processing, bank management, and auto-precharge

- Latency minimized via parameterized pipelining

- Achieves high clock rates with minimal routing constraints

- Supports full-rate, half-rate and quarter-rate clock operation

- Multi-mode controller support

-

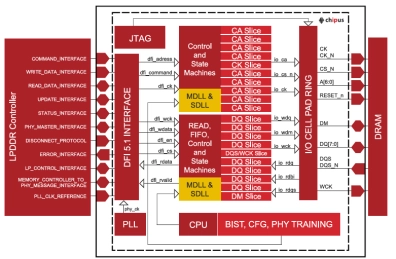

LPDDR4x/4 PHY IP for 22nm

- Compliant for JEDEC standards for LPDDR4x/4 with PHY standards

- DFI Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

LPDDR4/3, DDR4/3 Memory Controller IP

- Compliant with JEDEC standards for LPDDR4/3, DDR4/3

- DRAM rank of up to 4

- Lock-step-based controlling of multiple DRAM devices up to x64 DQ width

- Support for dynamic DRAM frequency scaling

-

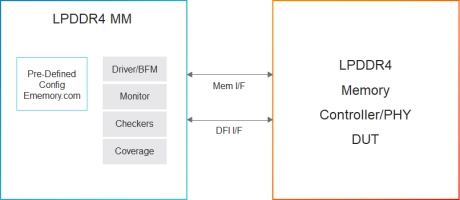

Simulation VIP for LPDDR4

- Speed (Mt/s)

- 2133MHz (4266MT/s)

- Device Density

- Supports a wide range of device densities from 4Gb to 32Gb

-

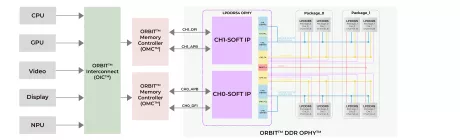

LPDDR4/4x/5/5x PHY

- Supports JEDEC SDRAM standards including LPDDR4 (1.1V), LPDDR4x (0.6V), LPDDR5/5x (0.5V)

- Supports data rates up to 4,266 Mbps LPDDR4/LPDDR5 and up to 8,533 Mbps LPDDR5x

- Support for 16, 32 and 64-bit operation

-

LPDDR4/4x IP solution

- Compatible with LPDDR4/4x up to 3733Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)

-

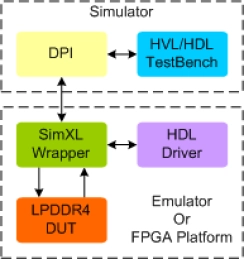

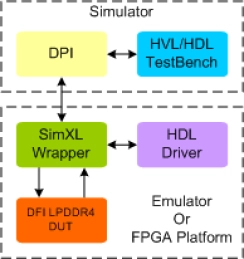

LPDDR4 Synthesizable Transactor

- Supports 100% of LPDDR4 protocol standard JESD209-4,JESD209-4A,JESD209-4B,JESD209-4C,JESD209-4D,JESD209-4X and JESD209-4Y (proposed)

- Supports all the LPDDR4 commands as per the specs

- Supports memory densities upto 32GB

- Supports device types X8 and X16

-

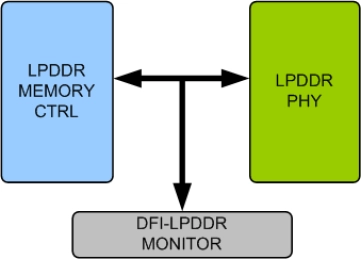

LPDDR4 DFI Synthesizable Transactor

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports LPDDR4 devices compliant with JEDEC LPDDR4 SDRAM Standard JESD209-4, JESD209-4A, JESD209-4B, JESD209-4C (Proposed), JESD209-4X and LPDDR4Y (Proposed).

- Supports for Read data-eye training

- Supports for Read gate training

-

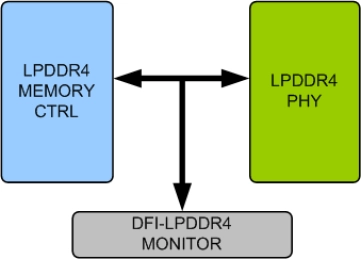

LPDDR4 DFI Verification IP

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports LPDDR4 devices compliant with JEDEC LPDDR4 SDRAM Standard JESD209-4, JESD209-4A, JESD209-4B, JESD209-4C (Proposed), JESD209-4X and LPDDR4Y (Proposed).

- Supports for Read data-eye training

- Supports for Read gate training

-

LPDDR DFI Verification IP

- Compliant with DFI version 2.0 or higher Specifications.

- Supports LPDDR devices compliant with JEDEC LPDDR SDRAM Standard JESD209A-1.pdf and JESD209B.pdf

- Supports all Interface Groups.

- Supports Write Transactions with Data mask