A 55nm Wirebond IO library with 1-3.3V GPIO, 3.3V pulse-width modulation cell, I2C & SVID open-drain cells, 3.3V & 5V analog cells, OTP program cell & associated ESD

Key attributes of this IO library include dual independent IO supply rails (1.0V-3.3V & 3.3V) and power-on-control (POC) to place IOs in HiZ during power-down. The GPIO cell can be configured as input, output or open-drain with a Schmitt trigger input and optional internal 55K ohm pull-up or pull-down resistor. Cells for two independent IO supplies, core power, ground and isolated ground with built-in ESD are included. A specialty output cell with matched throughput timings for pulse-width modulation (PWM) applications, along with 5V OTP programming, I2C & SVID open-drain and 3.3V & 5V analog cells (and associated ESD) complement the GPIO offering. The library is enriched with filler, corner, and domain-break cells in digital and analog domains, allowing for flexible pad ring construction. ESD design levels are 2KV HBM and 500V CDM

1.0-3.3V GPIO With I2C Open Drain And 3.3V & 5V Analog Cells in 55nm

Overview

Key Features

- 1.0V-3.3V | 3.3V IO operation

- Dual independent IO rails

- Output enable / disable (HiZ when disabled)

- Power-down control (HiZ upon VDD disable)

- Schmitt trigger receiver

- 55K? selectable pull-up or pull-down resistor

- ESD: 2KV HBM, 500V CDM

- Silicon proven

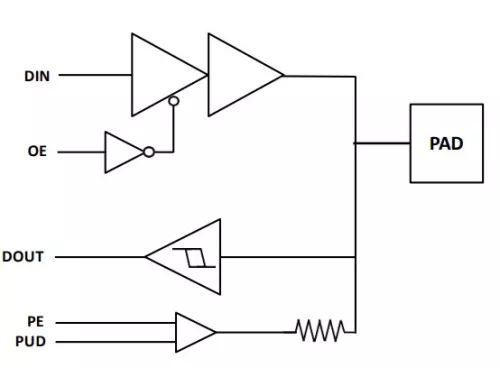

Block Diagram

Technical Specifications

Foundry, Node

TSMC 55nm

TSMC

Silicon Proven:

55nm

G

Related IPs

- 1.8V/3.3V Switchable GPIO With 5V I2C Open - Drain & Analog Cells in Samsung 11nm LPP

- 1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16/12nm

- 1.8V/3.3V Switchable GPIO With 3.3V I2C Open Drain & Analog in 22nm

- 28nm Wirebond IO library with dynamically switchable 1.8V/ 3.3V GPIO, 5V I2C open-drain, 1.8V & 3.3V analog, OTP program cell, and HDMI & LVDS protection macros - featured across a variety of metal stack and pad configuration options

- A 65nm Wirebond IO library with 1-3.3V GPIO, 3.3V pulse-width modulation cell, I2C & SVID open-drain, 3.3V & 5V analog and OTP program cell

- A 130nm Wirebond IO library with 3.3V GPIO, LVDS TX & RX, 3.3V I2C open-drain, analog cell and OTP program cell