VESA DSC IP

Welcome to the ultimate VESA DSC IP hub! Explore our vast directory of VESA DSC IP Cores

VESA DSC IP cores provide a low-latency, low-complexity codec specifically designed for data compression over the display interface.

VESA Display Compression Codecs (DSC) IP cores can compress any image to 8 bits per pixel (bpp), which results in a 3X compression ratio for a 24 bpp image or a 3.75X compression ratio for a 30 bpp image.

All offers in

VESA DSC IP

Filter

Compare

27

VESA DSC IP

from 10 vendors

(1

-

10)

-

VESA DSC 1.1 Encoder IP Core for Automotive Displays (ASIL-B Ready ISO 26262 Certified)

- VESA DSC 1.1 compliant

- Supports all DSC 1.1 mandatory encoding mechanisms

- Configurable maximum display resolution

-

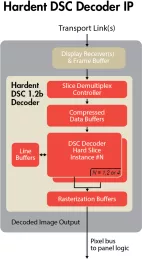

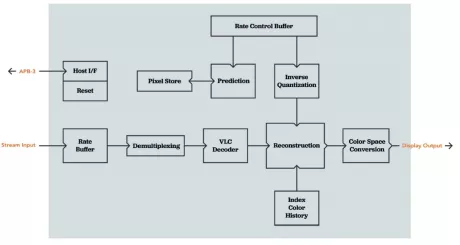

VESA DSC Decoder

- VESA Display Stream Compression (DSC) 1.2b compliant

- Supports all DSC 1.2b mandatory encoding mechanisms: MMAP, BP, MPP, and ICH

- Output buffering compatible with transport stream over video interfaces

- Configurable maximum display resolution

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, 12, 14, and 16 bits per video component

-

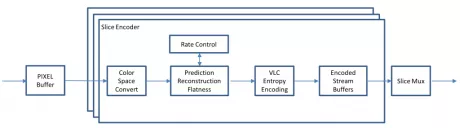

VESA DSC Encoder

- VESA Display Stream Compression (DSC) 1.2b compliant

- Supports all DSC 1.2b mandatory encoding mechanisms: MMAP, BP, MPP, and ICH

- Output buffering compatible with transport stream over video interfaces

- Configurable maximum display resolution

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, 12, 14, and 16 bits per video component

- YCbCr and RGB video input format

- 4:4:4, 4:2:2, and 4:2:0 native coding

-

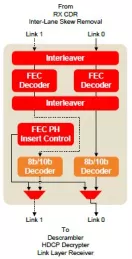

DisplayPort 1.4 FEC Receiver (Rx)

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

- Status and control can be done with signals or optionally via an integrated APB register module (Rx)

-

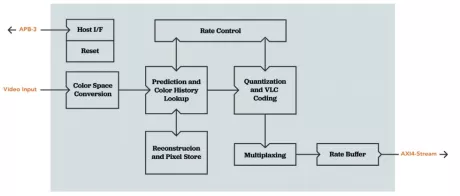

VESA Display Stream Compression (DSC) IP Core

- Supports Versions 1.1, 1.2 and 1.2a

- Supports RGB and YCbCr color spaces

- 1-to-8 slice support

-

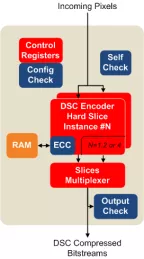

Display Stream Compression (DSC 1.2) Encoder

- VESA DSC 1.2 Compliant

- Capable of encoding up to 4K video at 30fps in FPGA and ASIC

- 8K compression available for select applications

-

Display Stream Compression (DSC 1.2) Decoder

- VESA DSC 1.2 Compliant

- Capable of decoding 4K video at 30fps in FPGA and ASIC

- Decode 8K video at 30fps in ASIC applications

-

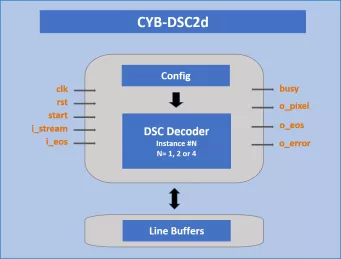

DSC Decoder

- Compliant with the VESA DSC 1.2a standards

- Perform encoding

- Support MMAP, BP, MPP and ICH

-

DSC Encoder

- Compliant with the VESA DSC 1.2a standards

- Perform encoding

- Support MMAP, BP, MPP and ICH

-

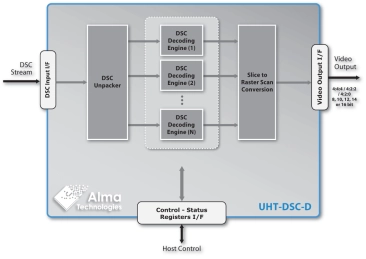

Scalable Ultra-High Throughput VESA DSC 1.2b Decoder

- The UHT-DSC-D core is a scalable, ultra-high throughput, advanced DSC 1.2b decoder, compliant to the VESA Display Stream Compression (DSC) 1.2b standard.

- It supports decoding of 4:4:4, 4:2:2 and 4:2:0 video streams, in 8 to 16 bits per component color depths.

- The core is designed for enabling ultra-high frame rate SD, HD and Ultra HD video decoding up to 10K resolutions, even in medium-end ASIC or FPGA silicon.