V-by-One IP

Welcome to the ultimate V-by-One IP hub! Explore our vast directory of V-by-One IP cores.

V-by-One® HS is a standard developed by THine Electronics to meet the needs of flat-panel display markets that require higher frame rates and higher resolutions than ever before.

All offers in

V-by-One IP

Filter

Compare

28

V-by-One IP

from 6 vendors

(1

-

10)

-

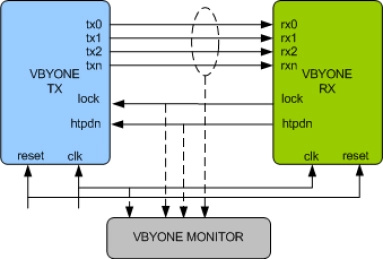

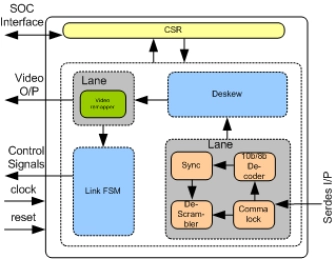

VBYONE Verification IP

- Follows VByOne specification as v1.2/1.3/1.4/1.5

- Support transmitter and Receiver Mode.

- Supports upto 32 serial lanes.

- Supports all byte lengths, color depths, and resolutions.

-

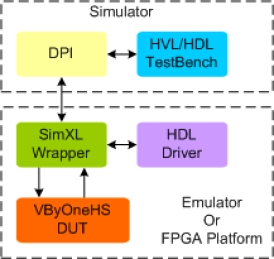

VBYONE Synthesizable Transactor

- Follows VByOne specification as 1.2/1.3/1.4/1.5

- Support transmitter and Receiver Mode

- Supports upto 32 serial lanes

- Supports all byte lengths, color depths, and resolutions

-

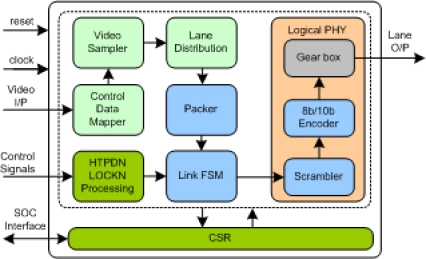

V-By-One Transmitter IIP

- Compliant with VByOne specification 1.2/1.3/1.4.

- Full VBYONE Transmit functionality.

- Supports 1 to 8 lanes. If needed, we can support custom lane configuration.

- Supports all byte lengths.

-

V-By-One Receiver IIP

- Compliant with VByOne specification 1.2/1.3/1.4.

- Full VBYONE Receive functionality.

- Supports 1 to 8 lanes. If needed, we can support custom lane configuration.

- Supports all byte lengths.

-

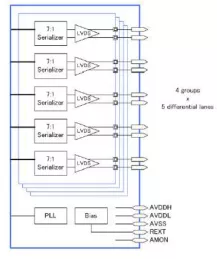

V-by-One/LVDS Tx Combo PHY, Silicon Proven in 28HPC+

- LVDS compliant Tx

- 4 groups of 4-Data

- 1-Clock channels Each lane/group can be turned on/off individually Data/Clock can be assigned to any lane within the group

- Differential polarity can be flip per lane

-

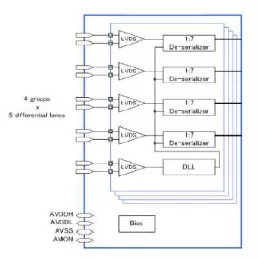

V-by-One/LVDS Rx IP, Silicon Proven in SMIC 40LL

- LVDS compliant Rx

- 4 groups of 4-Data, 1-Clock channels

- Each lane/group can be turned on/off individually

- Supports from 168Mbps to 1.5Gbps data rate

-

V-by-One/ LVDS Tx IP, Silicon Proven in SMIC 40LL

- LVDS compliant Tx

- 4 groups of 4-Data

- 1-Clock channels Each lane/group can be turned on/off individually Data/Clock can be assigned to any lane within the group

- Differential polarity can be flip per lane

-

V-by-One/LVDS Tx IP, Silicon Proven in GF 22FDX

- Support data rate: 0.6Gbps~4.0Gbps

- Utilize per-lane 10bit parallel interface

-

V-by-One/LVDS Rx IP, Silicon Proven in GF 22FDX

- LVDS compliant Rx

- 4 groups of 4-Data, 1-Clock channels

- Each lane/group can be turned on/off individually

- Supports from 168Mbps to 1.5Gbps data rate

-

V-by-One Rx IP, Silicon Proven in SMIC 40LL

- Wide-range data rate, up to 1Gbps, and the associated clock is DDR clock (1/2 of the data rate, up to 500MHz)

- 16 channels total 128 bits of parallel data, each channel has a bit width of 8 bits

- DC coupling mode

- Multi-channel shared offset