RapidIO IP

Welcome to the ultimate RapidIO IP hub! Explore our vast directory of RapidIO IP

All offers in

RapidIO IP

Filter

Compare

18

RapidIO IP

from 10 vendors

(1

-

10)

-

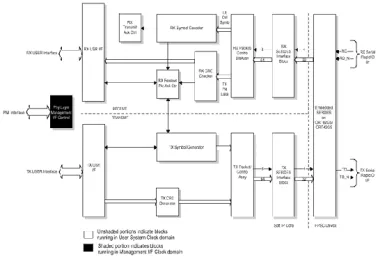

RapidIO Controller with V4.1 Support

- Compliant to RapidIO Specifications revision 4.1

- Compliant with RapidIO Error Management

- Extension specification, Revision 4.1

- Implements Logical, Transport and Physical layers functions

-

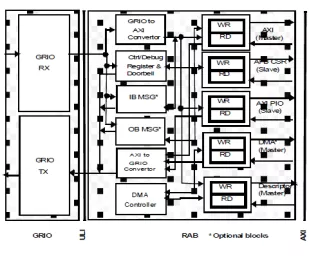

RapidIO to AXI Bridge (RAB)

- Compliant with RapidIO specification, Revision 4.0

- Compliant to AMBA AXI protocol v4

- Supports 32-bit or 38-bit addressing

- AXI PIO operation with configurable number of AXI Slaves

-

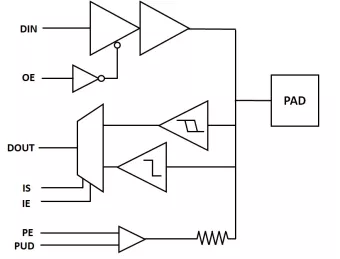

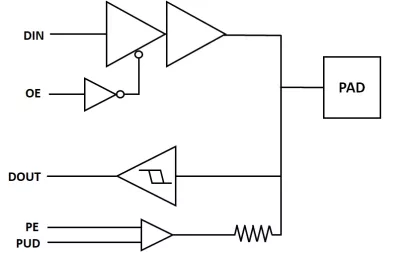

A 130nm Wirebond IO library with 3.3V GPIO, LVDS TX & RX, 3.3V I2C open-drain, analog cell and OTP program cell

- GPIO:

- I2C / SMBUS Open-Drain I/O:

- LVDS

- ANALOG

-

A 65nm Wirebond IO library with 1-3.3V GPIO, 3.3V pulse-width modulation cell, I2C & SVID open-drain, 3.3V & 5V analog and OTP program cell

- GPIO:

- I2C / SVID Open-Drain I/O:

- ANALOG

- OTP Programming Cell

-

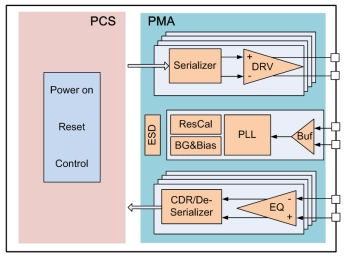

Rapid IO 4.0/3.1/2.2 PHY

- 4 Channel per Quad

- Shared Quad common PLL architecture

- Digitally-control-impedance termination resistors

- Configurable TX output differential voltage swing

-

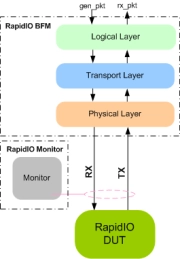

RapidIO Verification IP

- Supports RapidIO specification 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1.

- Supports Serial 1x/2x/4x/8x and 16x Physical lanes.

- Supports 8b/10b and 64b/67b Encode and Decode functions.

- Supports scrambler/Descrambler.

-

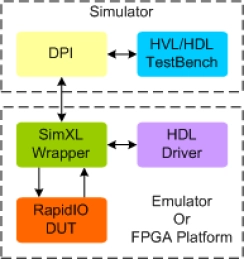

RapidIO Synthesizable Transactor

- Supports RapidIO specification 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1.

- Supports Serial 1x/2x/4x/8x and 16x Physical lanes.

- Supports 25.78125Gbaud/s, 12.5Gbaud/s, 10.3125Gbaud/s, 6.25Gbaud/s, 5Gbaud/s,3.125 Gbaud/s, 2.5 Gbaud/s, 1.25 Gbaud/s.

- 8b/10b Encode and Decode functions.

-

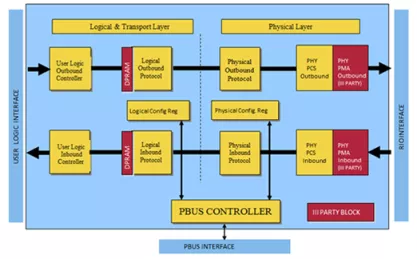

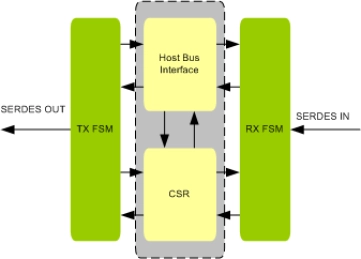

RAPIDIO EndPoint Controller IIP

- Compliant with RapidIO Interconnect 2.2 specification

- Supports all Capability Registers(CARs) and Configuration and Status Registers(CSRs)

- Supports high link utilization and low latency

- Supports efficient receive and transmit buffering scheme

-

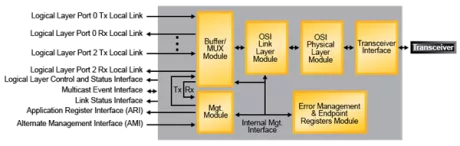

Serial RapidIO 2.1 Endpoint IP Core

- LatticeECP3 AMC Evaluation board

- Associated cables

- AMC interface card

- Demonstration bitstreams and files

-

Serial RapidIO - Physical Layer Interface

- Supports High Speed 1x Mode (up to 2.5 Gbps)

- 8B/10B Encoding and Decoding

- Clock and Data Recovery (CDR)

- Lane Synchronization