LIN IP

Welcome to the ultimate LIN IP hub! Explore our vast directory of LIN IP

All offers in

LIN IP

Filter

Compare

12

LIN IP

from 9 vendors

(1

-

10)

-

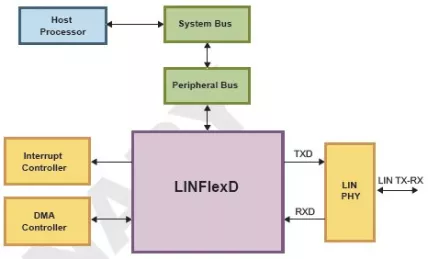

LINFlexD Controller

- Fractional baud rate generator

- Three operating modes for power saving

- Loopback mode for testing

-

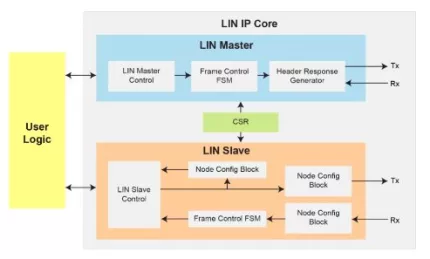

LIN Master Slave Controller

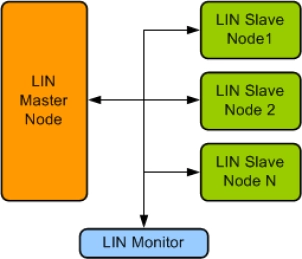

- LIN is a single wire-based interface, it reduces the cost and complexity of implementation.

- LIN is the best-suited and best alternative to CAN for applications that do not need high Bandwidth and that are of low speed.

- LIN is self-synchronized and therefore no need for external oscillators.

-

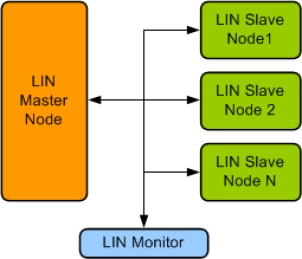

LIN Verification IP

- Compatible with Local Interconnect Network (LIN) specification versions 1.3,2.0,2.1 and 2.2A.

- Compliant with ISO 17987-3 and ISO 17987-6.

- Supports single Master and multiple Slaves.

- Supports test cases as per standard

-

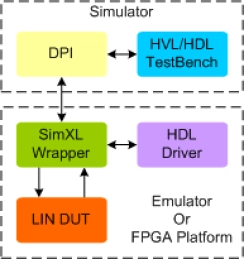

LIN Synthesizable Transactor

- Compatible with Local Interconnect Network (LIN) specifications version 2.2A

- Compliant with ISO/DIS 17987-2, ISO/DIS 17987-3 and ISO/DIS 17987-4

- Supports test cases as per standard

- INTERNATIONAL STANDARD ISO/DIS 17987-6

-

LIN Controller IIP

- Compliant with 2.2A LIN Specification

- Full LIN transmit and receive functionality

- Supports configurable master or slave functionality

- Supports all frame types

-

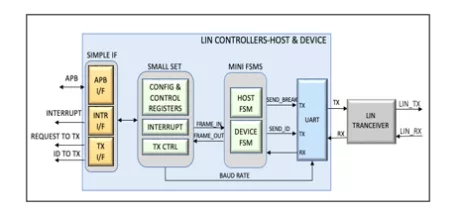

Host / Device LIN controller

- Implements the LIN 2.0, 2.1 and 2.2A protocols

- Backward Compatible to LIN 1.3

- Fully Programmable to operate in Host or Device Mode

- Simple interfaces to the system through AMBA-APB, AMBA-AHB or other SRAM like interfaces

-

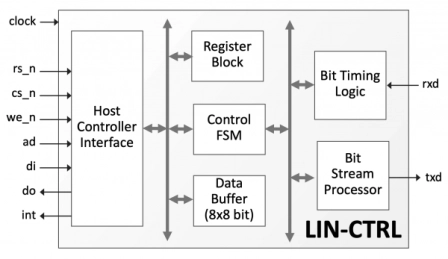

LIN 2.2, 2.1 and 1.3 Protocol Controller IP

- Conforms with LIN 1.2, LIN 2.1 and LIN 2.2 specification.

- Automatic LIN Header handling

- Automatic Re-synchronization

- Data rate between 1Kbit/s and 20 Kbit/s

-

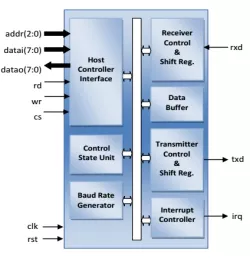

LIN Bus Master/Slave Controller

- Support of LIN specifications 2.0, 2.1, and 2.2A

- Backward compatible with LIN specification 1.3

- Run-time configurable master or slave operation

- Programmable data rate between 1 Kbit/s and 20 Kbit/s (for master)

-

LIN PHY

- driver

- EMC/ESD protection

- Full LIN functionality

-

LIN Bus Controller – Basic and Safety-Enhanced

- Conforms with LIN 1.2, LIN 2.1 and LIN 2.2 specification.

- Automatic LIN Header handling

- Automatic Re-synchronization

- Data rate between 1Kbit/s and 20 Kbit/s