Serdes IP for UMC

Welcome to the ultimate Serdes IP for UMC hub! Explore our vast directory of Serdes IP for UMC

All offers in

Serdes IP

for UMC

Filter

Compare

15

Serdes IP

for UMC

from 5 vendors

(1

-

10)

-

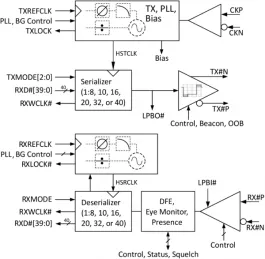

Multiprotocol SerDes PMA

- Supports over 30 protocols including CEI 6G & 11G SR, MR, LR, Ethernet 10GBASE-X/S/K/R, PCIe Gen1/2/3/4, V-by-One HS/US, CPRI, PON, OTN/OTU, 3GSDI, JESD204A/B/C, SATA1-3, XAUI, SGMII

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, or 40 bit

- Tx ring PLL includes fractional multiplication, spread spectrum and Jitter Cleaner function for Sync-E and OTU

- Core-voltage line driver with programmable pre-and post-emphasis

-

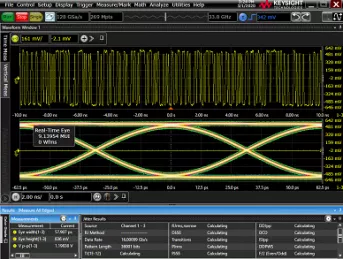

16Gbps multi-protocol programmable SerDes PHY in UMC 28HPC+

- Support PCIe G1 to G4 with PCS soft-macro supporting PIPE 4.4.1

- Support xPON applications: Sym/Asym GPON, Sym/Asym 10GPON, Sym EPON, Sym/Asym 10GEPON

-

XAUI PHY

- Idle is substituted as K,R or A in Transmit Direction

- K,R and A are substituted back to Idle in Receive Direction

-

10G Multi-SerDes PHY

- Reference Clock:

- Internal PLL:

- Data Transmit:

- Data Receive:

-

12.5G Multi-SerDes PHY

- Reference Clock:

- Internal PLL:

- Data Transmit:

- Data Receive:

-

25G Multi-SerDes PHY

- Reference Clock:

- Internal PLL:

- Data Transmit:

- Data Receive:

-

FPD-link, 30-Bit Color LVDS Receiver, 40-170Mhz (Full-HDTV @60Hz) LVDS SerDes 5:35 channel decompression with deskew capability

- Layout structure based on 1P6M, 1P7M, or 1P8M 0.13um Logic Salicide 1.2V/3.3V process.

- 1.2V/3.3V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3-1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 5.6Gbps bandwidth (40 to 170Mhz pixel clock) ( supports Full HDTV 1080p )

-

FPD-link, 30-Bit Color LVDS Receiver, 20-112Mhz (SVGA/WXGA/SXGA) LVDS SerDes 5:35 channel decompression

- Layout structure based on 1P6M, 1P7M, or 1P8M 0.13um Logic Salicide 1.2V/3.3V process.

- 1.2V/3.3V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3-1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 3.15Gbps bandwidth (20 to 90Mhz pixel clock)

-

Dual FPD-link, 30-Bit Color LVDS Transmitter, 40-170Mhz (Full-HD @120Hz) - with 2 independant links capability LVDS SerDes 70:10 channel compression

- 1P6M/1P7M/1P8M layout structure based on 0.13um Logic 1P8M Salicide 1.2V/3.3V process.

- 1.2V/3.3V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3-1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 11.9Gbps bandwidth (40 to 170Mhz pixel clock) per pixel channel (Full HD @ 120Hz)

-

GPON ONT SERDES (90nm UMC)

- Receiver capable of operating at 2.488Gbps (and 1.244Gbps for testing).

- Transmitter capable of operating at 1.244Gbps (and 2.488Gbps for testing).

- Jitter generation, jitter tolerance and jitter transfer are in compliance with the GPON standard.

- Programmable TX output amplitude level.