MIPI M-PHY IP for SMIC

Welcome to the ultimate MIPI M-PHY IP for SMIC hub! Explore our vast directory of MIPI M-PHY IP for SMIC

All offers in

MIPI M-PHY IP

for SMIC

Filter

Compare

7

MIPI M-PHY IP

for SMIC

from 3 vendors

(1

-

7)

-

MIPI M-PHY in SMIC 90LL

- Supports MIPI Standard for M-PHY v3.0.

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

-

MIPI M-PHY in SMIC 130nm

- Complies with MIPI Standard for M-PHY v3.0

- Slew-rate control for EMI reduction

- Supports HS modes GEAR 1-3

-

MIPI M-PHY Compliant (HS-G2) IP

- Complies with MIPI Standard for M-PHY, Draft Specification v0.90.

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports all HS modes (GEAR 1-2)

-

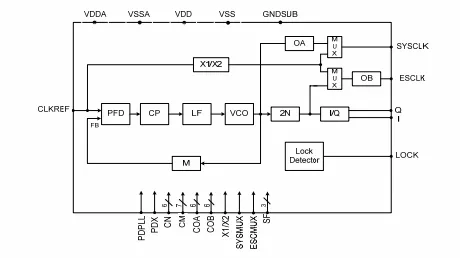

MIPI PLL

- All output programmable dividers produce 50% duty cycle for both even and odd divisors

- High performance, highly programmable MIPI Pixel PLL

- Digital CMOS process

- Low power dissipation

-

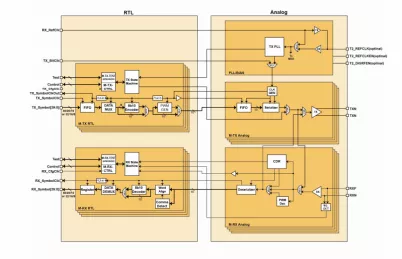

MIPI M-PHY DigRF Compliant IP

- Complies with MIPI Standard for M-PHY, Draft Specification v0.90.00- r02 and DigRF v4 V1.10.00.0.04

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports HS mode (GEAR 1-2, A & B)

-

MIPI M-PHY TX/RX + Controller

- Compliant with MIPI Alliance Standard for MIPI M-PHY V4.1 Specifications

- Supports standard RMMI interface compliant to M-PHY Specifications

- Supports HS Mode (GEAR1~4, A/B)

- Supports data rate up to 11.6608Gbps per lane

-

MIPI M-PHY v3.1 IP in TSMC(12/16nm, 28nm, 40nm, and 55nm)

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions